#### PATENT ABSTRACTS OF JAPAN

(11)Publication number:

2002-368428

(43)Date of publication of application: 20.12.2002

(51)Int.Cl.

H05K 3/46 H01L 23/12

(21)Application number: 2001-176350

(71)Applicant:

SONY CORP

(22)Date of filing:

11.06.2001

(72)Inventor:

OGAWA TAKESHI

OKUHORA AKIHIKO NAKAYAMA HIROKAZU

# (54) BOARD UNIT FOR HIGH-FREQUENCY MODULE, HIGH-FREQUENCY MODULE UNIT AND THEIR MANUFACTURING METHODS

#### (57)Abstract:

PROBLEM TO BE SOLVED: To reduce in size and cost of a package by thinning the package with a high accuracy and a high function. SOLUTION: A board unit for a high-frequency module comprises a base board 2 formed by flattening an uppermost layer by multilayer wiring on an organic base board 5 to a build-up forming surface 3, and a high-frequency circuit 4 formed with multilayer wiring layers 32 and 34 having passive elements via insulating layers 31 and 33 according to a thin film technique and a thick film technique on the build-up forming surface 3. An inductor element 37 for a high frequency is formed in an inner layer side wiring layer 31 of the circuit 4, and an inductor element 338 for a low frequency is formed in the front layer side wiring layer 34 formed thicker than the inner layer side wiring layer 31.

# LEGAL STATUS

[Date of request for examination]

[Date of sending the examiner's decision of rejection]

[Kind of final disposal of application other than the examiner's decision of rejection or application converted registration]

[Date of final disposal for application]

[Patent number]

[Date of registration]

[Number of appeal against examiner's decision of rejection]

[Date of requesting appeal against examiner's decision of rejection]

[Date of extinction of right]

# (19)日本国特許庁 (JP) (12) 公開特許公報 (A)

(11)特許出願公開番号 特期2002-368428 (P2002-368428A)

(43)公開日 平成14年12月20日(2002.12.20)

| (51) Int.Cl. <sup>7</sup> | 識別記号                        | FΙ             | テーマコート <sup>*</sup> (参考)   |

|---------------------------|-----------------------------|----------------|----------------------------|

| H05K 3/46                 |                             | H05K 3/46      | Q 5E346                    |

|                           |                             |                | В                          |

|                           |                             |                | L                          |

|                           |                             |                | U                          |

| H01L 23/12                |                             | H01L 23/12     | 301J                       |

|                           | 審査請求                        | 未請求 請求項の数56    | OL (全 25 頁) <b>最終</b> 頁に続く |

| (21)出願番号                  | 特顧2001-176350(P2001-176350) | (71)出顧人 000002 | 185                        |

|                           |                             | ソニー            | 株式会社                       |

| (22)出顧日                   | 平成13年6月11日(2001.6.11)       | 東京都            | 品川区北品川6丁目7番35号             |

|                           |                             | (72)発明者 小川     |                            |

|                           |                             | 東京都            | 品川区北品川6丁目7番35号 ソニ          |

|                           |                             | 一株式            | 会社内                        |

|                           |                             | (72)発明者 奥洞     | 明彦                         |

|                           |                             | 東京都            | 品川区北品川6丁目7番35号 ソニ          |

|                           |                             | 一株式            | 会社内                        |

|                           |                             | (74)代理人 100067 | 736                        |

|                           |                             | 弁理士            | 小池 晃 (外2名)                 |

|                           |                             |                |                            |

|                           |                             |                | 最終頁に続く                     |

# (54) 【発明の名称】 高周波モジュール用基板装置、高周波モジュール装置及びこれらの製造方法

# (57)【要約】

【課題】 高精度、高機能で薄型化され、パッケージの 小型化、低価格を図るようにする。

【解決手段】 有機ベース基板5に多層配線を行い最上 層を平坦化してビルドアップ形成面3としたベース基板 部2と、ビルドアップ形成面3上に薄膜技術や厚膜技術 により絶縁層31、33を介して受動素子を有する多層 の配線層32,34を形成した高周波回路部4とからな る。高周波回路部4の内層側配線層31に高周波用イン ダクタ素子37が成膜形成されるとともに内層側配線層 31よりも層厚に形成される表層側配線層34に低周波 用インダクタ素子38が成膜形成される。

#### 【特許請求の範囲】

【請求項1】 ベース基板の主面上に多層の配線層が形成されるとともに平坦な最上層の主面がビルドアップ形成面を形成してなるベース基板部と、

1

上記ベース基板部のビルドアップ形成面上にビルドアップ形成された多層の配線部からなり、それぞれの配線部 に誘電絶縁層を介して配線パターンが形成されるととも に受動素子が成膜形成されてなる高周波回路部とから構成され

上記高周波回路部には、内層側の配線部内に高周波帯域 用のインダクタ素子が成膜形成されるとともに、上記内 層側配線部よりも層厚とされた表層側の配線部内に低周 波帯域用のインダクタ素子が成膜形成されることを特徴 とする高周波モジュール用基板装置。

【請求項2】 有機基板からなるベース基板の主面上に 多層の配線層が形成されるとともに、その最上層に平坦 化処理を施してビルドアップ形成面を形成してなるベー ス基板部と、

上記ベース基板部のビルドアップ形成面上にビルドアップ形成された多層の配線部からなり、それぞれの配線部 20 に誘電絶縁層を介して配線パターンが形成されるとともに受動素子が成膜形成されてなる高周波回路部とから構成され、

上記高周波回路部には、内層側の配線部内に高周波帯域 用のインダクタ素子が成膜形成されるとともに、上記内 層側配線部よりも層厚とされた表層側の配線部内に低周 波帯域用のインダクタ素子が成膜形成されることを特徴 とする高周波モジュール用基板装置。

【請求項3】 上記ベース基板が、ポリフェニールエチレン、ビスマレイドトリアジン、ポリイミド、液晶ポリマ、ポリノルボルネン、ベンゾシクロブテンを基材として形成された両面基板、セラミックと有機材料の混合物によって形成された両面基板或いはエポキシ系両面基板から選択される有機基板であることを特徴とする請求項2に記載の高周波モジュール用基板装置。

【請求項4】 上記高周波回路部の誘電絶縁層が、ポリフェニールエチレン、ビスマレイドトリアジン、ポリイミド、液晶ポリマ、ポリノルボルネン、ベンゾシクロブテンから選択される有機材、エポキシ系樹脂材、アクリル系樹脂材によって形成されることを特徴とする請求項 401又は請求項2に記載の高周波モジュール用基板装置。

【請求項5】 上記高周波回路部の配線部は、上記配線パターンが銅パターンによって形成されることを特徴とする請求項1又は請求項2に記載の高周波モジュール用基板装置。

【請求項6】 上記高周波回路部の配線部は、上記内層側配線部のパターンが薄膜技術によって形成された薄膜の銅パターンであるとともに、上記表層側配線部のパターンが厚膜技術によって形成された厚膜の銅パターンであることを特徴とする請求項5に記載の高周波モジュー 50

ル用基板装置。

【請求項7】 上記高周波回路部の内層側配線部には、 上記誘電絶縁層上に薄膜形成技術によって薄膜抵抗体素 子部を形成し、この薄膜抵抗体素子部の一部を陽極酸化 法により酸化物化することによって薄膜キャパシタ素子 の高誘電膜として薄膜キャパシタ素子と薄膜抵抗体素子 とが形成されることを特徴とする請求項1又は請求項2 に記載の高周波モジュール用基板装置。

【請求項8】 上記高周波回路部の内層側配線部には、上記誘電絶縁層上に薄膜形成技術によって薄膜抵抗体素子部を形成し、この薄膜抵抗体素子部の全面が陽極酸化法により酸化されてなる酸化薄膜が薄膜キャパシタ素子の高誘電膜と上記薄膜抵抗体素子の保護膜としてパターニングされることにより、薄膜キャパシタ素子と薄膜抵抗体素子とが同時工程で形成されることを特徴とする請求項1又は請求項2に記載の高周波モジュール用基板装置

【請求項9】 上記薄膜抵抗体層を構成する薄膜が、窒化タンタル又はタンタルであることを特徴とする請求項7又は請求項8に記載の高周波モジュール用基板装置。

【請求項10】 上記高周波回路部には、上記表層側配線部の誘電絶縁層上に形成された配線パターンの入出力端子部を外方に露出させて保護層が形成されることを特徴とする請求項1又は請求項2に記載の高周波モジュール用基板装置。

【請求項11】 上記ベース基板には、上記ビルドアップ形成面と対向する第2の主面に電源入力端子部や信号入出力端子部を有する配線パターンが形成されるとともに、これら入出力端子部を外方に露出させて保護層が形成されることを特徴とする請求項1又は請求項2に記載の高周波モジュール用基板装置。

【請求項12】 上記保護層が、上記配線部の誘電絶縁層と同一材料又はソルダレジストによって形成されることを特徴とする請求項10又は請求項11に記載の高周波モジュール用基板装置。

【請求項13】 有機基板からなるベース基板の主面上に多層の配線層が形成されるとともに平坦化された最上層の主面がビルドアップ形成面を構成しかつこのビルドアップ形成面と対向する第2の主面に電源入力端子部や信号入力端子部を有する配線パターンが形成されてなるベース基板部と、このベース基板部の上記ビルドアップ形成面上にビルドアップ形成された多層の配線部からなりそれぞれの配線部に誘電絶縁層を介して配線パターンが形成されるとともに受動素子が成膜形成されてなる高周波回路部とから構成された高周波モジュール基板の表層側配線部の誘電絶縁層上に形成された配線パターンの入出力端子部と接続されて実装された少なくとも1個以上の高周波集積回路素子と、

上記高周波モジュール基板の第2の主面に形成された上

記配線パターンの入力端子部が接続されることによって 上記高周波モジュール基板を実装するマザー基板とを備 え、

上記高周波回路部には、内層側の配線部内に高周波帯域 用のインダクタ素子が成膜形成されるとともに、上記内 層側配線部よりも層厚とされた表層側の配線部内に低周 波帯域用のインダクタ素子が成膜形成されることを特徴 とする高周波モジュール装置。

【請求項14】 上記高周波モジュール基板のベース基板が、ポリフェニールエチレン、ビスマレイドトリアジ 10 ン、ポリイミド、液晶ポリマ、ポリノルボルネン、ベンゾシクロブテンを基材として形成された両面基板、セラミックと有機材料の混合物によって形成された両面基板或いはエポキシ系両面基板から選択される有機基板であり、

主面上に多層に形成された配線層の最上層が平坦化処理 を施されて平坦なビルドアップ形成面として構成される ることを特徴とする請求項13に記載の高周波モジュー ル装置。

【請求項15】 上記高周波モジュール基板の高周波回路部が、上記誘電絶縁層を、ポリフェニールエチレン、ビスマレイドトリアジン、ポリイミド、液晶ポリマ、ポリノルボルネン、ベンゾシクロブテンから選択される有機材、エポキシ系樹脂材、アクリル系樹脂材によって形成されることを特徴とする請求項13に記載の高周波モジュール装置。

【請求項16】 上記高周波モジュール基板の高周波回路部が、上記配線部の配線パターンを銅パターンによって形成されることを特徴とする請求項13に記載の高周波モジュール装置。

【請求項17】 上記高周波モジュール基板の高周波回路部が、上記内層側配線部の銅パターンを薄膜技術によって形成されるとともに、上記表層側配線部の銅パターンが厚膜技術によって形成されることを特徴とする請求項16に記載の高周波モジュール装置。

【請求項18】 上記高周波モジュール基板の高周波回路部には、上記内層側配線部に、上記誘電絶縁層上に薄膜形成技術により薄膜抵抗体素子部を形成し、この薄膜抵抗体素子部の一部を陽極酸化法によって酸化物化して薄膜キャパシタ素子の高誘電膜とすることにより、薄膜40キャパシタ素子と薄膜抵抗体素子とが形成されることを特徴とする請求項13に記載の高周波モジュール装置。

【請求項19】 上記高周波モジュール基板の高周波回路部には、内層側配線部に、上記誘電絶縁層上に薄膜形成技術により薄膜抵抗体素子部を形成し、この薄膜抵抗体素子部の全面が陽極酸化法によって酸化されてなる酸化薄膜が薄膜キャパシタ素子の高誘電膜と前記薄膜抵抗体素子の保護膜としてパターニングされることによって、薄膜キャパシタ素子と薄膜抵抗体素子とが同時工程で形成されることを特徴とする請求項13に記載の高周50

波モジュール装置。

【請求項20】 上記薄膜抵抗体層を構成する薄膜が、 窒化タンタル又はタンタルであることを特徴とする請求 項18又は請求項19に記載の高周波モジュール装置。

4

【請求項21】 上記高周波モジュール基板の高周波回路部には、上記表層側配線部に形成された上記配線パターンの入出力端子部を外方に露出させる保護層が形成されることを特徴とする請求項13に記載の高周波モジュール装置。

【請求項22】 上記高周波モジュール基板のベース基板には、上記第2の主面に形成された上記配線パターンの入出力端子部を外方に露出させて保護層が形成されることを特徴とする請求項13に記載の高周波モジュール装置。

【請求項23】 上記保護層が、上記配線部の誘電絶縁層と同一材料又はソルダレジストによって形成されることを特徴とする請求項21又は請求項22に記載の高周波モジュール装置。

【請求項24】 上記高周波モジュール基板の高周波回20 路部には、上記高周波集積回路素子を含んで全面を覆うシールドカバーが取り付けられていることを特徴とする請求項13に記載の高周波モジュール装置。

【請求項25】 上記高周波モジュール基板の高周波回路部には、上記高周波集積回路素子とシールドカバーとの間に、熱伝導性を有する樹脂材が充填されていることを特徴とする請求項13に記載の高周波モジュール装置

【請求項26】 上記高周波モジュール基板の高周波回路部には、上記高周波集積回路素子の搭載領域に対応位置して上記ベース基板に貫通する多数個の放熱ビアホールが形成され、

上記ベース基板には上記各放熱ビアホールが接続される 放熱手段が設けられていることを特徴とする請求項13 に記載の高周波モジュール装置。

【請求項27】 上記放熱手段が、上記ベース基板に形成された厚みが大きな放熱パターンによって構成されることを特徴とする請求項26に記載の高周波モジュール装置。

【請求項28】 上記ベース基板が、金属板を内蔵した 多層基板からなり、上記金属板が放熱手段を構成することを特徴とする請求項26に記載の高周波モジュール装置

【請求項29】 少なくとも一方主面上に多層の配線層が形成されてなる多層基板からなるベース基板の最上層に平坦化処理を施して平坦なビルドアップ形成面を形成する工程を有するベース基板部製作工程と、

上記ベース基板のビルドアップ形成面上に、それぞれ誘電絶縁層を介して配線パターンを形成するとともに受動素子を成膜形成してなる配線部を多層に形成して高周波回路部をビルドアップ形成する高周波回路部製作工程と

を有し、

上記高周波回路部製作工程において、内層側配線部の形 成工程では上記誘電絶縁層上に高周波帯域用のインダク タ素子が成膜形成されるとともに、上記表層側配線部の 形成工程では上記内層側配線部の誘電絶縁層よりも層厚 とされた上記誘電絶縁層上に低周波帯域用のインダクタ 素子が成膜形成されることを特徴とする高周波モジュー ル用基板装置の製造方法。

【請求項30】 上記ベース基板部製作工程における上 記ビルドアップ形成面の平坦化処理工程が、表層配線層 10 を覆って樹脂付銅箔を貼り合わせる工程と、上記樹脂付 銅箔に上記高周波回路部との接続用のビアホールを形成 する工程とを経て、表面研磨法によって上記表層配線層 の表面電極部を露出させるように上記樹脂付銅箔を研磨 する工程であることを特徴とする請求項29に記載の高 周波モジュール用基板装置の製造方法。

【請求項31】 上記ベース基板部製作工程における最 上層の平坦化処理工程が、表層配線層の全面を絶縁樹脂 で被覆する工程と、表面研磨によって上記表層配線層の 表面電極部を露出させるように上記絶縁樹脂層を研磨す る工程であることを特徴とする請求項29に記載の高周 波モジュール用基板装置の製造方法。

【請求項32】 上記高周波回路部製作工程において、 上記内層側配線部のパターンを絶縁樹脂層上に薄膜技術 によって薄膜の銅パターンとして形成する工程と、上記 表層側配線部のパターンを絶縁樹脂層上に厚膜技術によ って厚膜の銅パターンとして形成する工程とを有するこ とを特徴とする請求項29に記載の髙周波モジュール用 基板装置の製造方法。

【請求項33】 上記高周波回路部製作工程における内 層側配線部の形成工程が、下層の配線層上に誘電絶縁材 によって誘電絶縁層を形成する工程と、上記誘電絶縁層 の所定位置に層間接続ビアホールを形成する工程と、上 記誘電絶縁層上に薄膜形成技術により薄膜抵抗体素子を 形成する工程と、この薄膜抵抗体素子の一部を陽極酸化 法により酸化膜化する工程とを有し、

上記酸化膜を薄膜キャパシタ素子の高誘電膜として、同 時工程で上記内層側配線部内に薄膜キャパシタ素子と薄 膜抵抗体素子とを形成することを特徴とする請求項29 に記載の高周波モジュール用基板装置の製造方法。

【請求項34】 上記高周波回路部製作工程における内 層側配線部の形成工程が、下層の配線層上に誘電絶縁材 によって誘電絶縁層を形成する工程と、上記誘電絶縁層 の所定位置に層間接続ビアホールを形成する工程と、上 記誘電絶縁層上に薄膜形成技術により薄膜抵抗体素子を 形成する工程と、この薄膜抵抗体素子の全面を陽極酸化 法により酸化膜化する工程とを有し、

上記酸化膜を薄膜キャパシタ素子の高誘電膜と上記薄膜 抵抗体素子の保護膜として、同時工程で上記内層側配線 部内に薄膜キャパシタ素子と薄膜抵抗体素子とを形成す 50 ことを特徴とする請求項39に記載の髙周波モジュール

ることを特徴とする請求項29に記載の高周波モジュー ル用基板装置の製造方法。

【請求項35】 上記上記高周波回路部製作工程におい て、上記各配線部の誘電絶縁層を、ポリフェニールエチ レン、ビスマレイドトリアジン、ポリイミド、液晶ポリ マ、ポリノルボルネン、ベンゾシクロブテンから選択さ れる有機材、エポキシ系樹脂材、アクリル系樹脂材によ って形成することを特徴とする請求項29に記載の高周 波モジュール用基板装置の製造方法。

【請求項36】 上記高周波回路部の表層配線部上にそ の配線パターンの入出力端子部を外方に露出させる保護 層を形成する保護層形成工程を有することを特徴とする 請求項29に記載の髙周波モジュール用基板装置の製造 方法。

【請求項37】 上記ビルドアップ形成面と対向する第 2の主面に電源入力端子部や信号入出力端子部を有する 配線パターンが形成された上記ベース基板に、上記入出 力端子部を外方に露出させる保護層を形成する保護層形 成工程を有することを特徴とする請求項29に記載の高 周波モジュール用基板装置の製造方法。

【請求項38】 上記保護層を、上記各配線部の誘電絶 縁層に用いられるポリフェニールエチレン、ビスマレイ ドトリアジン、ポリイミド、液晶ポリマ、ポリノルボル ネン、ベンゾシクロブテンから選択される有機材、エポ キシ系樹脂材、アクリル系樹脂材又はソルダレジストに よって形成することを特徴とする請求項36又は請求項 37に記載の高周波モジュール用基板装置の製造方法。

【請求項39】 上記高周波回路部の表層配線部に、誘 電絶縁層と所定の配線パターンを有する上部配線部を形 成する工程と、上記配線パターンの所定の電極部を露出 させて保護層を形成する工程とを有する上部配線部形成

上記上部配線部上に、上記電極部と接続される少なくと も 1 個以上の高周波集積回路素子を直接搭載する高周波 集積回路素子搭載工程とを有することを特徴とする請求 項29に記載の高周波モジュール用基板装置の製造方

【請求項40】 上記高周波集積回路素子とシールドカ バーとの間に熱伝導性樹脂材を充填する工程と、

上記高周波回路部に、上記高周波集積回路素子を含んで その全面を覆うシールドカバーを取り付けるシールドカ バー取付工程とを有することを特徴とする請求項39に 記載の高周波モジュール用基板装置の製造方法。

【請求項41】 上記高周波回路部製作工程において、 上記高周波集積回路素子の搭載領域に対応位置して上記 ベース基板に貫通する多数個の放熱ビアホールを形成す る工程を有し、

上記放熱ビアホールが、上記ベース基板部製作工程にお いて上記ベース基板に設けられた放熱手段と接続される

用基板装置の製造方法。

【請求項42】 上記ベース基板部製作工程において、 表層配線部に厚みが大きな放熱パターンを形成すること を特徴とする請求項41に記載の高周波モジュール用基 板装置の製造方法。

【請求項43】 少なくとも一方主面上に多層の配線層が形成されてなる多層有機基板からなるベース基板の最上層に平坦化処理を施して平坦なビルドアップ形成面を形成する工程を有するベース基板部製作工程と、

上記ベース基板部のビルドアップ形成面上に、それぞれ 誘電絶縁層を介して配線パターンを形成するとともに受 動素子を成膜形成してなる配線部を多層に形成してなる 高周波回路部がビルドアップ形成され、内層側配線部に は上記誘電絶縁層上に高周波帯域用のインダクタ素子を 成膜形成するとともに、上記表層側配線部には上記内層 側配線部の誘電絶縁層よりも層厚とされた上記誘電絶縁 層上に低周波帯域用のインダクタ素子を成膜形成する高 周波回路部製作工程とを経て高周波モジュール基板を製 作する高周波モジュール基板製作工程と、

上記ベース基板のビルドアップ形成面と対向する第2の 主面に形成された入出力端子部に対応して主面上に接続 端子部が形成されたマザー基板に対して、相対する上記 入出力端子部と接続端子部とを接続することにより上記 高周波モジュール基板を実装する高周波モジュール実装 工程とを有することを特徴とする高周波モジュール装置 の製造方法。

【請求項44】 上記ベース基板部製作工程における上記ビルドアップ形成面の平坦化処理工程が、表層配線層を覆って樹脂付銅箔を貼り合わせる工程と、上記樹脂付銅箔に上記高周波回路部との接続用のビアホールを形成する工程とを経て、表面研磨法によって上記表層配線層の表面電極部を露出させるように上記樹脂付銅箔を研磨する工程であることを特徴とする請求項43に記載の高周波モジュール装置の製造方法。

【請求項45】 上記ベース基板部製作工程における最上層の平坦化処理工程が、表層配線層の全面を絶縁樹脂で被覆する工程と、表面研磨によって上記表層配線層の表面電極部を露出させるように上記絶縁樹脂層を研磨する工程であることを特徴とする請求項43に記載の高周波モジュール装置の製造方法。

【請求項46】 上記高周波回路部製作工程において、 上記内層側配線部のパターンを絶縁樹脂層上に薄膜技術 によって薄膜の銅パターンとして形成する工程と、上記 表層側配線部のパターンを絶縁樹脂層上に厚膜技術によ って厚膜の銅パターンとして形成する工程とを有するこ とを特徴とする請求項43に記載の高周波モジュール装 置の製造方法。

【請求項47】 上記高周波回路部製作工程における内層側配線部の形成工程が、下層の配線層上に誘電絶縁材によって誘電絶縁層を形成する工程と、上記誘電絶縁層 50

の所定位置に層間接続ビアホールを形成する工程と、上 記誘電絶縁層上に薄膜形成技術により薄膜抵抗体素子を 形成する工程と、この薄膜抵抗体素子の一部を陽極酸化 法により酸化膜化する工程とを有し、

上記酸化膜を薄膜キャパシタ素子の高誘電膜として、同時工程で上記内層側配線部内に薄膜キャパシタ素子と薄膜抵抗体素子とを形成することを特徴とする請求項43 に記載の高周波モジュール装置の製造方法。

【請求項48】 上記高周波回路部製作工程における内層側配線部の形成工程が、下層の配線層上に誘電絶縁材によって誘電絶縁層を形成する工程と、上記誘電絶縁層の所定位置に層間接続ビアホールを形成する工程と、上記誘電絶縁層上に薄膜形成技術により薄膜抵抗体素子を形成する工程と、この薄膜抵抗体素子の全面を陽極酸化法により酸化膜化する工程とを有し、

上記酸化膜を薄膜キャパシタ素子の高誘電膜と上記薄膜 抵抗体素子の保護膜として、同時工程で上記内層側配線 部内に薄膜キャパシタ素子と薄膜抵抗体素子とを形成す ることを特徴とする請求項43に記載の高周波モジュー 20 ル装置の製造方法。

【請求項49】 上記上記高周波回路部製作工程において、上記各配線部の誘電絶縁層を、ポリフェニールエチレン、ビスマレイドトリアジン、ポリイミド、液晶ポリマ、ポリノルボルネン、ベンゾシクロブテンから選択される有機材、エポキシ系樹脂材、アクリル系樹脂材によって形成することを特徴とする請求項43に記載の高周波モジュール装置の製造方法。

【請求項50】 上記高周波回路部の表層配線部上にその配線パターンの入出力端子部を外方に露出させる保護層を形成する保護層形成工程を有することを特徴とする請求項43に記載の高周波モジュール装置の製造方法。

【請求項51】 上記ビルドアップ形成面と対向する第2の主面に電源入力端子部や信号入出力端子部を有する配線パターンが形成された上記ベース基板に、上記入出力端子部を外方に露出させる保護層を形成する保護層形成工程を有することを特徴とする請求項43に記載の高周波モジュール装置の製造方法。

【請求項52】 上記保護層を、上記各配線部の誘電絶縁層に用いられるポリフェニールエチレン、ビスマレイドトリアジン、ポリイミド、液晶ポリマ、ポリノルボルネン、ベンゾシクロブテンから選択される有機材、エポキシ系樹脂材、アクリル系樹脂材又はソルダレジストによって形成することを特徴とする請求項50又は請求項51に記載の高周波モジュール装置の製造方法。

【請求項53】 上記高周波回路部の表層配線部に、誘電絶縁層と所定の配線パターンを有する上部配線部を形成する工程と、上記配線パターンの所定の電極部を露出させて保護層を形成する工程とを有する上部配線部形成工程と、

上記上部配線部上に、上記電極部と接続される少なくと

7

30

10

も1個以上の高周波集積回路素子を直接搭載する高周波 集積回路素子搭載工程とを有することを特徴とする請求 項43に記載の高周波モジュール装置の製造方法。

9

【請求項54】 上記高周波集積回路素子とシールドカバーとの間に熱伝導性樹脂材を充填する工程と、

上記高周波回路部に、上記高周波集積回路素子を含んでその全面を覆うシールドカバーを取り付けるシールドカバー取付工程とを有することを特徴とする請求項43に記載の高周波モジュール装置の製造方法。

【請求項55】 上記高周波回路部製作工程において、 上記高周波集積回路素子の搭載領域に対応位置して上記 ベース基板に貫通する多数個の放熱ビアホールを形成す る工程を有し、

上記放熱ビアホールが、上記ベース基板部製作工程において上記ベース基板に設けられた放熱手段と接続されることを特徴とする請求項43に記載の高周波モジュール装置の製造方法。

【請求項56】 上記ベース基板部製作工程において、表層配線部に厚みが50 um以上の放熱パターンを形成することを特徴とする請求項43に記載の高周波モジュ 20 ール装置の製造方法。

#### 【発明の詳細な説明】

#### [0001]

【発明の属する技術分野】本発明は、例えばパーソナルコンピュータ、オーディオ機器或いは各種のモバイル機器や携帯電話機等の各種電子機器等に好適に用いられ、情報通信機能やストレージ機能等を有して超小型通信機能モジュールを構成する高周波モジュール用基板装置とその製造方法及び高周波モジュール装置とその製造方法に関する。

#### [0002]

【従来の技術】例えば、音楽、音声或いは画像等の各種情報は、近年、データのデジタル化に伴ってパーソナルコンピュータやモバイルコンピュータ等によっても手軽に扱えるようになっている。また、これらの情報は、音声コーデック技術や画像コーデック技術により帯域圧縮が図られて、デジタル通信やデジタル放送により各種の通信端末機器に対して容易にかつ効率的に配信される環境が整いつつある。例えば、オーディオ・ビデオデータ(AVデータ)は、携帯電話機を介して屋内外での受信40も可能である。

【0003】ところで、データ等の送受信システムは、家庭を始めとして小規模な地域内においても好適なネットワークシステムの提案によって、様々に活用されるようになっている。ネットワークシステムとしては、例えばIEEE802.1aで提案されているような5GHz帯域の狭域無線通信システム、IEEE802.1bで提案されているような2.45帯域の無線LANシステム或いはBluetoohと称される近距離無線通信システム等の種々の次世代ワイヤレスシステムが注目されている。データ等の送受信シ 50

ステムは、かかるワイヤレスネットワークシステムを有効に利用して、家庭内や屋外等の様々な場所において手軽にかつ中継装置等を介することなく様々なデータの授受、インターネット網へのアクセスやデータの送受信が可能となる。

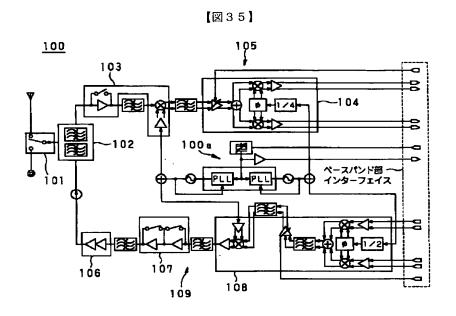

【0004】一方、データ等の送受信システムにおいては、小型軽量で携帯可能であり上述した通信機能を有する通信端末機器の実現が必須となる。通信端末機器においては、送受信部においてアナログの高周波信号の変復調処理を行うことが必要であることから、一般に図35に示すような送受信信号からいったん中間周波数に変換するようにしたスーパーへテロダイン方式による無線通信送受信回路100が備えられる。

【0005】無線通信送受信回路100には、アンテナや切替スイッチを有して情報信号を受信或いは送信するアンテナ部101と、送信と受信との切替を行う送受信切替器102とが備えられる。無線通信送受信回路100には、周波数変換回路部103や復調回路部104等からなる受信回路部105が備えられる。無線通信送受信回路100には、パワーアンプ106やドライブアンプ107及び変調回路部108等からなる送信回路部109が備えられる。無線通信送受信回路100には、受信回路部105や送信回路部109に基準周波数を供給する基準周波数生成回路部100aが備えられる。

【0006】かかる無線通信送受信回路100においては、詳細を省略するが、各段間にそれぞれ介挿された種々のフィルタ、局発装置(VCO:voltage contolled oscillator)、SAWフィルタ(saw tooth waveform filter)等の大型機能部品や、整合回路或いはバイアス回路等の高周波アナログ回路に特有なインダクタ、抵抗、キャパシタ等の受動部品の点数が非常に多い構成となっている。無線通信送受信回路100においては、各回路部のIC化が図られるが、各段間に介挿されるフィルタをIC中に取り込むことが困難であり、またこのために整合回路も外付けとして必要となる。したがって、無線通信送受信回路100は、全体に大型となり、通信端末機器の小型軽量化に大きな障害となっていた。

【0007】一方、通信端末機器には、図36に示すように中間周波数への変換を行わずに情報信号の送受信を行うようにしたダイレクトコンバージョン方式による無線通信送受信回路110においては、アンテナ部111によって受信された情報信号が送受信切替器112を介して復調回路部113に供給されて直接ベースバンド処理が行われる。無線通信送受信回路110においては、ソース源で生成された情報信号が変調回路部114において中間周波数に変換されることなく直接所定の周波数帯域に変調され、アンプ115と送受信切替器112を介してアンテナ部111から送信される。

【0008】かかる無線通信送受信回路110は、情報

信号について中間周波数の変換を行うことなくダイレク ト検波を行うことによって送受信する構成であることか ら、フィルタ等の部品点数が低減されて全体構成の簡易 化が図られ、より1チップ化に近い構成が見込まれるよ うになる。しかしながら、無線通信送受信回路110に おいても、後段に配置されたフィルタ或いは整合回路の 対応が必要となる。また、無線通信送受信回路110に おいては、高周波段で一度の増幅を行うことから充分な ゲインを得ることが困難となり、ベースバンド部でも増 幅操作を行う必要がある。したがって、無線通信送受信 10 回路110は、DCオフセットのキャンセル回路や余分 なローパスフィルタを必要とし、さらに全体の消費電力 が大きくなるといった問題がある。

#### [0009]

【発明が解決しようとする課題】従来の無線通信送受信 回路は、上述したようにスーパーヘテロダイン方式及び ダイレクトコンバージョン方式のいずれにおいても、通 信端末機器の小型軽量化等の要求仕様に対して充分な特 性を満足し得ないものであった。このため、無線通信送 受信回路については、例えばSi-CMS回路等をベー スとして簡易な構成によって小型化を図ったモジュール 化について種々の試みが図られている。すなわち、試み の1つは、例えば特性の良い受動素子をSi基板上に形 成するとともにフィルタ回路や共振器等をLSI上に作 り込み、さらにベースバンド部分のロジックLSIも集 積化することによって、いわゆる1チップ化高周波送受 信モジュールを製作する方法である。

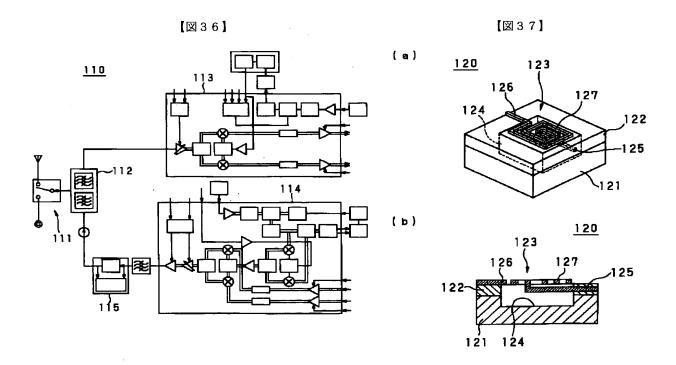

【0010】しかしながら、かかるSi基板高周波送受 信モジュールにおいては、いかにして特性の良い受動素 子、特にインダクタをLSI上に形成するかが極めて重 30 要となる。例えば図37に示した髙周波送受信モジュー ル120においては、Si基板121及びSiО₂絶縁 層122のインダクタ形成部位123に対応して大きな 凹部124を形成してなる。高周波送受信モジュール1 20は、凹部124に臨ませて第1の配線層125を形 成するとともに凹部124を閉塞する第2の配線層12 6が形成されてインダクタ部127を構成する。

【0011】高周波送受信モジュール120は、上述し たようにインダクタ部127を凹部124に臨ませて空 中に浮かせた構成となっており、これによって回路内干 40 渉が低減されて特性向上が図られてなる。しかしなが ら、高周波送受信モジュール120は、インダクタ部1 27を形成する工程が極めて面倒であり、工程数も増加 してコストアップとなるといった問題があった。

【0012】また、高周波送受信モジュールにおいて は、他の対応として配線パターンの一部を基板表面から 立ち上げて空中に浮かすといった対応を図ることによっ てインダクタ部を形成する対応も図られている。 しかし ながら、かかる髙周波送受信モジュールも、インダクタ 部を形成する工程が極めて面倒であり、工程の増加によ 50 を有しないガラス基板141を用いることで、ガラス基

ってコストがアップするといった問題があった。

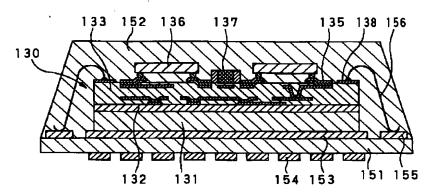

【0013】一方、1チップ化高周波送受信モジュール においては、アナログ回路の高周波回路部と、デジタル 回路のベースバンド回路部との間に介在するSi基板の 電気的干渉が大きな問題となる。このため、高周波送受 信モジュールについては、例えば図38に示したSi基 板高周波送受信モジュール130や、図39に示したガ ラス基板高周波送受信モジュール140が提案されてい

12

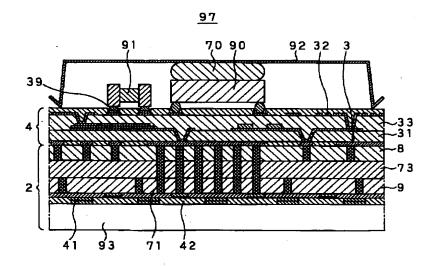

【0014】高周波送受信モジュール130は、Si基 板131上にSiO2層132を形成した後に、リソグ ラフィ技術によって受動素子形成層133が成膜形成さ れてなる。高周波送受信モジュール130は、受動素子 形成層133の内部に、詳細を省略するが配線パターン とともにインダクタ部、抵抗体部或いはキャパシタ部等 の受動素子が薄膜形成技術や厚膜形成技術によって多層 に形成されている。髙周波送受信モジュール130は、 受動素子形成層133上に中継スルーホールとなるビア ホール134等を介して層内配線パターンと接続された 端子部135が形成され、これら端子部135にフリッ プチップ実装法等により高周波ICやLSI等の回路素 子136が直接実装されて構成される。

【0015】高周波送受信モジュール130は、例えば ベースバンド回路部を設けたマザー基板等に実装するこ とにより、Si基板131により高周波回路部とベース バンド回路部とを区分して両者間の電磁的干渉を抑制す ることが可能とされるようになる。しかしながら、かか る高周波送受信モジュール130においては、導電性を 有するSi基板131が受動素子形成層133内に精度 の高い各受動素子を形成するために有効に機能するが、 このSi基板131が各受動素子の良好な高周波特性に とって邪魔になり特性が劣化するといった問題がある。

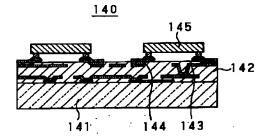

【0016】一方、高周波送受信モジュール140は、 上述した高周波送受信モジュール130のSi基板13 1に起因する問題を解決するために、ベース基板にガラ ス基板141が用いられて構成されている。高周波送受 信モジュール140も、ガラス基板141上にリソグラ フィ技術によって受動素子形成層142が成膜形成され てなる。 高周波送受信モジュール140にも、詳細を省 略するが受動素子形成層142の内部に、配線パターン とともにインダクタ部、抵抗体部或いはキャパシタ部等 の受動素子が薄膜形成技術や厚膜形成技術によって多層 に形成されている。高周波送受信モジュール140は、 受動素子形成層142上にビアホール143等を介して 内部配線パターンと接続された端子部144が形成さ れ、これら端子部144にフリップチップ実装法等によ り高周波ICやLSI等の回路素子145が直接実装さ れて構成される。

【0017】高周波送受信モジュール140は、導電性

板141と受動素子形成層142との容量的結合度が抑 制され受動素子形成層142内に良好な高周波特性を有 する受動素子を形成することを可能とする。高周波送受 信モジュール140は、例えばマザー基板等に実装する ために、受動素子形成層142の表面に端子パターンを 形成するとともにワイヤボンディング法等によってマザ 一基板との接続が行われる。したがって、高周波送受信 モジュール140は、端子パターン形成工程やワイヤボ ンディング工程が必要となり、また小型化にも不利とな る。

【0018】1チップ化高周波送受信モジュールにおい ては、上述したようにベース基板上に高精度の受動素子 形成層が形成される。ベース基板には、受動素子形成層 を薄膜形成する際に、スパッタリング時の表面温度の上 昇に対する耐熱特性、リソグラフィ時の焦点深度の保 持、マスキング時のコンタクトアライメント特性が必要 となる。ベース基板は、このために高精度の平坦性が必 要とされるとともに、絶縁性、耐熱性或いは耐薬品性等 が要求される。

【0019】Si基板131やガラス基板141は、か かる特性を有しておりLSIと別プロセスにより低コス トで低損失な受動素子の形成を可能とする。また、Si 基板131やガラス基板141は、従来のセラミックモ ジュール技術で用いられる印刷によるパターン等の形成 方法或いはプリント配線基板に配線パターンを形成する 湿式エッチング法等と比較して、高精度の受動素子の形 成が可能であるとともに、素子サイズをその面積が1/ 100程度まで縮小することを可能とする。さらに、S i基板131やガラス基板141は、受動素子の使用限 界周波数帯域を20GHzまで高めることも可能とす る。

【0020】しかしながら、かかる髙周波送受信モジュ ールにおいては、上述したようなSi基板131やガラ ス基板141上に形成した配線層を介して高周波信号系 のパターン形成と、電源やグランド部の供給配線或いは 制御系信号配線が行われる。高周波送受信モジュールに おいては、このために各配線間に電気的干渉が生じると ともに、配線層を多層に形成することによるコストアッ プの問題が生じる。

【0021】さらに、上述した高周波送受信モジュール 40 130、140は、図40に示すようにインターポーザ 基板151上に搭載されてパッケージ150を形成す る。パッケージ150は、インターポーザ基板151の 一方主面上に高周波送受信モジュール130を搭載する とともに全体を絶縁樹脂152によって封装してなる。 パッケージ150は、インターポーザ基板151の表裏 主面にパターン配線層153や入出力端子154をそれ ぞれ形成するとともに、高周波送受信モジュール130 の搭載領域の周囲に多数の電極部155が形成されてな

【0022】パッケージ150は、インターポーザ基板 151上に高周波送受信モジュール130を搭載した状 態で、この高周波送受信モジュール130と電極部15 5とをワイヤボンディング法によりワイヤ156によっ て電気的に接続して電源供給や信号の送受を行うように する。したがって、高周波送受信モジュール130に は、高周波IC136やチップ部品137等を実装した 表面層に、端子部135とともに実装部品を接続する配 線パターンやワイヤ156が接続される電極138等が 10 形成される。なお、髙周波送受信モジュール140につ いても、同様にしてパッケージ化が図られる。

【0023】高周波送受信モジュール130、140 は、上述したようにインターポーザ基板151上に搭載 されてパッケージ化が図られるが、パッケージ150の 厚みや面積を大きくさせるといった問題があった。ま た、高周波送受信モジュール130、140は、パッケ ージ150のコストをアップさせるといった問題もあ

【0024】また、パッケージ150には、高周波送受 信モジュール130、140に搭載した高周波ICやL SI等の回路素子を覆って、電磁波ノイズの影響を低減 するシールドカバーが取り付けられる。パッケージ15 0において、回路素子から発生する熱がシールドカバー 内にこもって特性を劣化させることから、放熱構造を設 ける必要がある。パッケージ150においては、高周波 送受信モジュール130、140にSi基板121やガ ラス基板131が用いられることによって、これら基板 側からの放熱を行う放熱構造を設けることが困難である とともに大型化するといった問題もある。さらに、パッ ケージ150は、高周波送受信モジュール130、14 0に比較的高価なSi基板121やガラス基板131が 用いられることで、コストがアップするといった問題が あった。

【0025】したがって、本発明は、ベース基板上に高 精度の受動素子や高密度配線層を形成して高精度化及び 薄型化、小型化、低価格化を図り、特に周波数帯域に応 じてインダクタ素子の機能特性がそれぞれに発揮される ようにする髙周波モジュール用基板装置とその製造方法 及び高周波モジュール装置とその製造方法を提供するこ とを目的に提案されたものである。

#### [0026]

30

【課題を解決するための手段】上述した目的を達成する 本発明に係る高周波モジュール用基板装置は、ベース基 板の主面上に多層の配線層が形成されるとともに平坦な 最上層の主面がビルドアップ形成面を形成してなるベー ス基板部と、このベース基板部のビルドアップ形成面上 にビルドアップ形成された多層の配線部からなりそれぞ れの配線部に誘電絶縁層を介して配線パターンが形成さ れるとともに受動素子が成膜形成されてなる高周波回路 部とから構成される。高周波モジュール用基板装置に

は、高周波回路部の内層側配線部内に高周波帯域用のインダクタ素子が成膜形成されるとともに、内層側配線部よりも層厚とされた表層側配線部内に低周波帯域用のインダクタ素子が成膜形成されてなる。

【0027】また、本発明に係る高周波モジュール用基板装置は、有機基板からなるベース基板の主面上に多層の配線層が形成されるとともにその最上層に平坦化処理を施してビルドアップ形成面を形成してなるベース基板部と、このベース基板部のビルドアップ形成面上にビルドアップ形成された多層の配線部からなりそれぞれの配線部に誘電絶縁層を介して配線パターンが形成されるとともに受動素子が成膜形成されてなる高周波回路部の内層側配線部内に高周波帯域用のインダクタ素子が成膜形成されてなる。

【0028】以上のように構成された本発明に係る高周波モジュール用基板装置によれば、層薄の内層側配線部をベースとして表層側配線部を積層形成することから高精度の高周波回路部を形成することが可能となる。また、高周波モジュール用基板装置によれば、内層側配線部内に高周波帯域用のインダクタ素子を成膜形成し、表層側配線部内に充分な厚みを有する低周波帯域用のインダクタ素子が成膜形成される。

【0029】インダクタ素子は、形成される配線部の層の厚みが大きいほど損失が少なく高いQ値(共振バロメータ)を出力して特性の向上が図られるようになる。一方、インダクタ素子は、表皮効果によって、周波数に依存する表皮効果厚み以上では伝播損失がほとんど変化しない特性を有している。インダクタ素子の表皮効果厚みは、周波数が高ければ高いほど小さくなる。

【0030】したがって、高周波モジュール用基板装置によれば、薄膜の内層側配線部内に成膜形成された高周波帯域用のインダクタ素子と、厚膜の表層側配線部内に充分な厚みを有して成膜形成された低周波帯域用のインダクタ素子とが、高周波信号と低周波信号とにそれぞれ適応したインダクタとして機能する。高周波モジュール用基板装置によれば、かかる構成によって小型化、薄型化が図られるとともに高精度化及び高機能化が図られる40ようになる。

【0031】また、高周波モジュール用基板装置によれば、ベース基板として比較的廉価な有機基板を用いることで、全体コストの低減が図られる。また、高周波モジュール装置によれば、ベース基板部を電源やグランド部の配線部や制御系の配線部として構成することにより、高周波回路部との電気的分離が図られるようになる。したがって、高周波モジュール装置によれば、高周波回路部の電気的干渉の発生が抑制されて特性の向上が図られ、また充分な面積を有する電源やグランド部の配線が50

ベース基板部に形成することが可能であることからレギ ュレーションの高い電源供給が行われるようになる。

【0032】また、上述した目的を達成する本発明に係 る高周波モジュール用基板装置の製造方法は、少なくと も一方主面上に多層の配線層が形成されてなる多層基板 からなるベース基板の最上層に平坦化処理を施して平坦 なビルドアップ形成面を形成する工程を有するベース基 板部製作工程と、ベース基板のビルドアップ形成面上に それぞれ誘電絶縁層を介して配線パターンを形成すると ともに受動素子を成膜形成してなる配線部を多層に形成 して高周波回路部をビルドアップ形成する高周波回路部 製作工程とを有する。高周波モジュール用基板装置の製 造方法においては、高周波回路部製作工程において、内 層側配線部の形成工程で誘電絶縁層上に高周波帯域用の インダクタ素子を成膜形成するとともに、表層側配線部 の形成工程で内層側配線部の誘電絶縁層よりも層厚とさ れた誘電絶縁層上に低周波帯域用のインダクタ素子を成 膜形成する。

【0033】上述した工程を有する本発明に係る高周波 モジュール用基板装置の製造方法によれば、平坦化され たビルドアップ形成面上に層薄の内層側配線部を形成 し、この内層側配線部をベースとして表層側配線部を積 層形成することから高精度の高周波回路部を積層形成す ることが可能となる。高周波モジュール用基板装置の製 造方法によれば、内層側配線部内に高周波帯域用のイン ダクタ素子を成膜形成するとともに表層側配線部内に充 分な厚みを有する低周波帯域用のインダクタ素子を成膜 形成することから、各インダクタ素子が高周波信号と低 周波信号とにそれぞれ適応したインダクタとして機能す る小型化、薄型化が図られるとともに高精度化及び高機 能化が図られた高周波モジュール用基板装置の製造を可 能とする。髙周波モジュール用基板装置の製造方法によ れば、ベース基板として比較的廉価な有機基板を用いる ことで、全体コストの低減が図られる。また、高周波モ ジュール装置の製造方法によれば、ベース基板部を電源 やグランド部の配線部や制御系の配線部として構成する ことにより、電気的分離が図られた高周波回路部の電気 的干渉の発生が抑制されて特性の向上が図られ、また充 分な面積を有する電源やグランド部の配線がベース基板 部に形成することが可能であることからレギュレーショ ンの高い電源供給が行われるようになる高周波モジュー ル装置を製造することが可能とする。

【0034】さらに、上述した目的を達成する本発明に係る高周波モジュール装置は、高周波モジュール基板と、この高周波モジュール基板の表層側配線部の誘電絶縁層上に形成された配線パターンの入出力端子部と接続されて実装された少なくとも1個以上の高周波集積回路素子と、高周波モジュール基板の第2の主面に形成された配線パターンの入力端子部が接続されることによって高周波モジュール基板を実装するマザー基板とを備えて

なる。高周波モジュール基板は、有機基板からなるベース基板の主面上に多層の配線層が形成されるとともにで、 坦化された最上層の主面がビルドアップ形成面を構成で、 かつこのビルドアップ形成面と対向する第2の主面にで、 源入力端子部や信号入力端子部を有する配線パターンが形成面上にビルドアップ形成された多層の配線部からなりそれぞれの配線部に誘電絶縁層を介して配線のからなりをれぞれの配線部に透りを表子が成膜形成されるとともに、内層側配線部よりも層厚とされた表層側の配線部内に低周波帯域用のインダクタ素子が成膜形成されてなる。

17

【0035】以上のように構成された本発明に係る高周 波モジュール装置には、ベース基板部の平坦なビルドア ップ形成面上に層薄の内層側配線部が形成されこの内層 側配線部をベースとして表層側配線部を積層形成するこ とから高精度かつ薄型に形成された高周波回路部を有す る髙周波モジュール基板が備えられる。また、高周波モ ジュール装置には、内層側配線部内に高周波帯域用のイ ンダクタ素子を成膜形成するとともに表層側配線部内に 充分な厚みを有する低周波帯域用のインダクタ素子を成 膜形成することにより各インダクタ素子が高周波信号と 低周波信号とにそれぞれ適応したインダクタとして機能 する高周波回路部を有する高機能かつ高性能の高周波モ ジュール基板が備えられる。さらに、高周波モジュール 装置は、廉価な有機基板からなるベース基板部が充分な 面積を有する電源やグランド部の配線部や制御系の配線 部として構成され、このベース基板部と高精度に形成さ れた高周波回路部との電気的分離を図って電気的干渉の 発生を抑制し特性の向上を図った高周波モジュール基板 が備えられる。

【0036】高周波モジュール装置は、上述した特性を有する高周波モジュール基板に高周波集積回路素子が直接搭載されるとともに、これをマザー基板に実装して構成される。したがって、高周波モジュール装置は、高精度化及び薄型化、小型化、低価格化を図った通信モジュールパッケージを構成し、携帯型電子機器等に好適に用いたれる。

【0037】さらにまた、上述した目的を達成する本発明に係る高周波モジュール装置の製造方法は、ベース基板部製作工程と高周波回路部製作工程とからなる高周波モジュール基板製作工程と、高周波モジュール実装工程とを有する。高周波モジュール基板製作工程のベース基板部製作工程は、少なくとも一方主面上に多層の配線層が形成されてなる多層有機基板からなるベース基板の最上層に平坦化処理を施して平坦なビルドアップ形成面を形成する。高周波モジュール基板製作工程の高周波回路部製作工程は、ベース基板部のビルドアップ形成面上

に、それぞれ誘電絶縁層を介して配線パターンを形成するとともに受動素子を成膜形成してなる配線部を多層に形成してなる高周波回路部をビルドアップ形成する。高周波回路部製作工程では、内層側配線部の誘電絶縁層上に高周波帯域用のインダクタ素子を成膜形成するととと表層側配線部の誘電絶縁層上に低周波帯域用のインダクタ素子を成膜形成する。高周波モジュール装置の製造方法は、高周波モジュール実装工程が、ベース基板部の大アップ形成面と対向する第2の主面に形成された入出力端子部に対応して主面上に接続端子部が形成されたマザー基板に対して、相対する上記入出力端子部と接続端子部とを接続することにより高周波モジュール基板が実装される。

18

【0038】以上の工程を有する本発明に係る高周波モ ジュール装置の製造方法によれば、ベース基板部の平坦 なビルドアップ形成面上に層薄の内層側配線部が形成さ れこの内層側配線部をベースとして表層側配線部を積層 形成することから高精度かつ薄型に形成された高周波回 路部を有する高周波モジュール基板が製作される。ま た、高周波モジュール装置の製造方法によれば、内層側 配線部内に高周波帯域用のインダクタ素子を成膜形成す るとともに表層側配線部内に充分な厚みを有する低周波 帯域用のインダクタ素子を成膜形成することにより各イ ンダクタ素子が高周波信号と低周波信号とにそれぞれ適 応したインダクタとして機能する高周波回路部を有する 高機能かつ高性能の高周波モジュール基板が製作され る。さらに、高周波モジュール装置の製造方法によれ ば、廉価な有機基板からなるベース基板部が充分な面積 を有する電源やグランド部の配線部や制御系の配線部と して構成されて、このベース基板部と高精度に形成され た高周波回路部との電気的分離を図って電気的干渉の発 生を抑制し特性の向上を図った高周波モジュール基板が 製作される。髙周波モジュール装置の製造方法によれ ば、上述した高特性を有する高周波モジュール基板に高 周波集積回路素子が直接形成されて搭載されるととも に、これをマザー基板に実装することから、高精度化及 び薄型化、小型化、低価格化が図られ、携帯型電子機器 等に好適に用いられる通信モジュールパッケージの製造 40 が可能となる。

#### [0039]

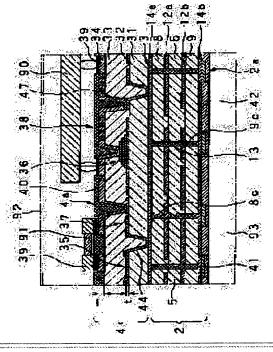

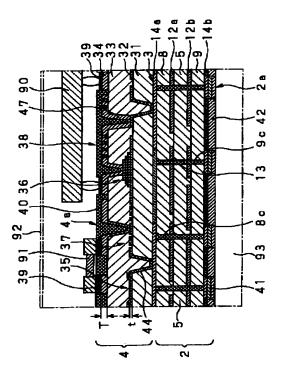

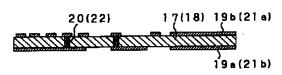

【発明の実施の形態】以下、本発明の実施の形態について、図面を参照して詳細に説明する。実施の形態として図1に示した高周波モジュール用基板装置(以下、モジュール基板と略称する。)1は、ベース基板部製作工程によって最上層が高精度の平坦面に形成されてビルドアップ形成面3として構成されたベース基板部2と、このベース基板部2をベースとして高周波回路部製作工程によってビルドアップ形成面3上に積層形成された高周波回路部4とから構成される。

【0040】モジュール基板1は、ベース基板部2が、ビルドアップ形成面3上に形成された高周波回路部4に対する電源系や制御系の配線部或いはマザー基板93に対する実装面を構成している。モジュール基板1には、図1に示すように、高周波回路部4の表面4aを実装面として高周波IC90やチップ部品91が実装されるとともに、シールドカバー92が組み付けられて表面全体が封装される。モジュール基板1は、いわゆる1チップ部品としてマザー基板93上に実装され、携帯機器等に好適に用いられて無線送受信機能を奏する高周波モジュール装置94を構成する。

【0041】ベース基板部2は、図3に示す両面基板からなるベース基板5をコアとして、後述する各工程を経てその第1の主面5a側に高周波回路部4が積層形成される第1のパターン配線層6が形成される。ベース基板部2は、ベース基板5の第1の主面5a及び第2の主面5bに電源回路部やグランド部等を構成する第1のパターン配線層6及び第2のパターン配線層7が形成されるとともに、第2のパターン配線層7がマザー基板93への実装部を構成する。

【0042】ベース基板部2には、ベース基板5に対して第1の樹脂付銅箔8乃至第4の樹脂付銅箔11が接合される。第1の樹脂付銅箔8は、図5に示すようにベース基板5の第1の主面5a側に接合されてこのベース基板5とともに、ベース基板部2に2層の第1のパターン配線層6を形成する。第2の樹脂付銅箔9は、同図に示すようにベース基板5の第2の主面5b側に接合されてこのベース基板5とともに、ベース基板部2に2層の第2のパターン配線層7を形成する。第3の樹脂付銅箔10と第4の樹脂付銅箔11は、それぞれ第1のパターン配線層6と第2のパターン配線層7とに接合される。

【0043】ベース基板5には、低誘電率で低いTan δ、すなわち高周波特性に優れかつ耐熱温度が160℃ 以上である有機基材、例えばポリフェニールエチレン (PPE)、ビスマレイドトリアジン(BT-resi n)、ポリテトラフルオロエチレン(商標名テフロ ン)、ポリイミド、液晶ポリマ(LCP)、ポリノルボ ルネン(PNB)、ガラスエポキシ、フェノール樹脂、 ポリオレフィン、セラミック或いはセラミックと有機基 材の混合体等からなる基材が用いられて形成される。べ 40 ース基板5は、機械的剛性とともに耐熱性、耐薬品性を 有し、例えば上述した基材よりもさらに廉価なエポキシ 系基板FR-5等を用いてもよい。ベース基板5は、上 述した一般的な配線基板装置に用いられる廉価な有機基 材を素材として形成されるが、高精度に形成されること によって比較的高価となるSi基板やガラス基板と比較 して廉価であり材料コストの低減が図られる。勿論、べ ース基板5は、素材としてSi基板やガラス基板を用い てもよい。

【0044】ベース基板部2の構成並びに製作工程につ 50

いて、以下図2に示した製作工程図及び図3乃至図10を参照して詳細に説明する。ベース基板部製作工程は、図3に示すように表裏主面5a、5bに銅箔が接合されたベース基板5に、適宜のパターン形状の第1配線層12a、12bを形成する第1配線層形成工程s-1を第1の工程とする。ベース基板5には、ドリルやレーザによる孔穿加工が施されて所定の位置に複数個のビアホール13が形成される。ベース基板5には、メッキ等によって内壁に導通処理が施された各ビアホール13が形成される。ベース基板5には、メッキ等によって内壁に導通処理が施された各ビアホール13が形成される。ベース基板5には、銅箔層に対してフォトリソグラフ処理が施され、図4に示すように表裏主面5a、5bとにそれぞれ第1配線層12a、12bが形成される。第1配線層12a、12bが形成される。第1配線層12a、12bが形成の配線部或いはグランド面等を構成する。

【0045】ベース基板部製作工程は、図5に示すように第1配線層12a、12bが形成されたベース基板5の表裏主面5a、5bに、第1の樹脂付銅箔8と第2の樹脂付銅箔9とをそれぞれ接合する第1の樹脂付銅箔8及び第2の樹脂付銅箔9は、それぞれ銅箔層8a、9aの一方主面の全体に樹脂層8b、9bが裏打ちされてなり、樹脂層側を接合面としてベース基板5の表裏主面5a、5bとに接着樹脂(プリプレグ)によって接合される。なお、これら第1の樹脂付銅箔8及び第2の樹脂付銅箔9は、樹脂層8b、9bがLCP等の熱可塑性樹脂によって形成される場合には接着樹脂を不要としてベース基板5に接合される。

【0046】ベース基板部製作工程は、接合した第1の樹脂付銅箔8及び第2の樹脂付銅箔9に対して、図6に示すようにそれぞれ第1配線層12a、12bに接続される複数のビアホール8c、9cを形成するビアホール形成工程s-3を第3の工程とする。ビアホール形成工程s-3を第3の工程とする。ビアホール形成工程s-3においては、第1の樹脂付銅箔8及び第2の樹脂付銅箔9に対してフォトリソグラフ処理を施した後に湿式エッチングを行って図6に示すようにそれぞれ開口を形成し、これら開口をマスクとしてレーザ加工を施ですことによって第1配線層12a、12bの電極部が受けとなって各樹脂層8b、9bにそれぞれホールを施ではよって各樹脂層8b、9bにそれぞれホールを施では、各ホールにビアメッキ等により内壁に導通処理を施すとともにメッキ法や導電ペーストの埋め込みによって導電材が充填されてビアホール8c、9cを形成する。

【0047】ベース基板部製作工程は、第1の樹脂付銅箔8及び第2の樹脂付銅箔9の銅箔層8a、9aに所定のパターンからなる第2配線層14a、14bを形成する第2配線層形成工程s-4においては、銅箔層8a、9aに対してフォトリソグラフ処理を施こして、図7に示すように第2配線層14a、14bが形成されたベース基板

部中間体15を製作する。ベース基板部中間体15は、第2配線層14a、14bは、上述した第1配線層12a、12bと同様に電源系や制御系の配線部或いはグランド面等を構成する。ベース基板部中間体15には、表裏主面にそれぞれ第1配線層12aと第2配線層14aとの2層からなる第1のパターン配線層6と、第1配線層12bと第2配線層14bとの2層からなる第2のパターン配線層7とが形成されてなる。

【0048】ベース基板部製作工程においては、上述した工程を経て製作されたベース基板部中間体15の表裏 10 主面を高精度の平坦面とするための平坦化工程が施される。ベース基板部2は、後述するようにベース基板部中間体15の第1のパターン配線層6が高周波回路部4の実装面を構成する。ベース基板部2は、ベース基板5に有機基板を基材とした廉価な両面基板を用いて上述した工程を経てベース基板部中間体15を製作することから、ベース基板5の面精度が直接第1のパターン配線層6に転写されて高精度の平坦性が保持し得ない。

【0049】したがって、ベース基板部製作工程においては、ベース基板部中間体15の表裏主面を高精度の平坦面とする平坦化工程が施される。すなわち、ベース基板部製作工程は、ベース基板部中間体15の表裏主面に対して、図8に示すように第3の樹脂付銅箔10を第4の樹脂付銅箔11とを接合する第2の樹脂付銅箔接合工程をする。これら第3の樹脂付銅箔10及び第4の樹脂付銅箔9と同様に銅箔層10a、11aの一方主面の全体に樹脂層10b、11bが裏打ちされてなる。第3の樹脂付銅箔10及び第4の樹脂付銅箔11は、図9に示すように樹脂層10b、11b側を接合面として第2配線層14a、14b上にそれぞれ接着樹脂によって接合される。

【0050】ベース基板部製作工程は、第3の樹脂付銅箔10及び第4の樹脂付銅箔11に対して研磨処理を施こして最上層に高精度の平坦面としたビルドアップ形成面3を形成する研磨工程s-6を第6の工程とする。研磨工程s-6は、例えばアルミナとシリカの混合を納路はより第3の樹脂付銅箔10と第4の樹脂付銅箔11の全体を研磨することによってベース基板中間体15の表裏主面を精度の高い平坦面に形成する。の樹脂付銅箔10側、換言すればビルドアップ形成面3にでは第2配線層14aが外方に露出するまで研磨す。また、研磨工程s-6においては、第4の樹脂付っては第2配線層14bを外方に露出でが変調であるまで樹脂層11bに所定の厚み $\Delta$ xを残すようにして研磨を施す。

【0051】ベース基板部2は、上述したようにベース 板17には、同図に示すようにビアホール20aがそれ 基板5の主面5b側に第2配線層14bが形成されると ぞれ形成される。第1の回路パターン19aと第2の回 ともに、この第2配線層14bが第4の樹脂付銅箔11 50 路パターン19bとは、上述したベース基板部2の第1

の樹脂層11bの研削量を制限することによって外方に露出されない構造となっている。ベース基板部2は、かかる構成によって後述する高周波回路部製作工程において、誘電体層からなる樹脂層11bが第2配線層14bを薬品や機械的或いは熱的負荷から保護する。第2配線層14bは、高周波回路部4を形成した後に上述した樹脂層11bが外方に露出するまで切削除去され、マザー基板93上に形成した各電極部と接続されて入出力端子部を構成する。

【0052】ベース基板部製作工程は、上述した各工程によりベース基板5からベース基板中間体15を経て、良好な平坦精度を有するビルドアップ形成面3が形成されてなるベース基板部2を製作する。ベース基板部製作工程は、ベース基板中間体15を製作する工程を従来の多層基板の製作工程と同様とすることで、多層基板の製作プロセスをそのまま適用可能であるとともに、量産性も高い。なお、ベース基板部製作工程については、上述した工程に限定されるものではなく、従来採用されている種々の多層基板の製作工程が採用されてもよいことは勿論である。

【0053】なお、ベース基板部製作工程においては、ベース基板5に対して第2の樹脂付銅箔9を介して接合される第4の樹脂付銅箔11が、銅箔部11aを研磨されることになる。ベース基板部製作工程においては、接合された各構成部材がプレス機によってプレスされて一体化される。ベース基板部製作工程においては、金属製のプレス面と第4の樹脂付銅箔11とのなじみがよく、精度のよいプレスが行われるようになる。したがって、第4の樹脂付銅箔11については、銅箔部が配線層を構成しないことから、銅貼りでなく他の樹脂付金属箔であってもよい。

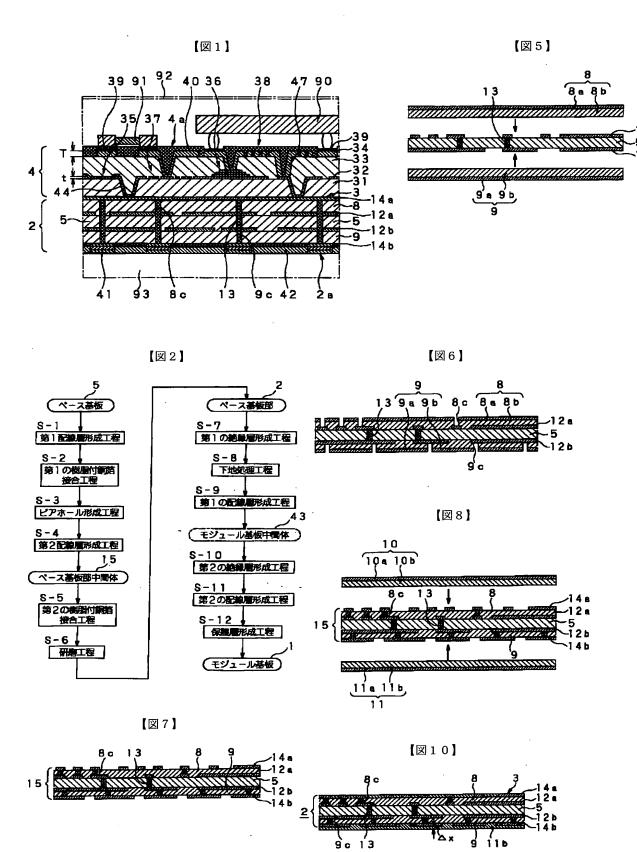

【0054】他の実施の形態として図11乃至図17に示したベース基板部製作工程は、2枚の両面基板17、18を用いて上述したベース基板部2と同様のベース基板部16を製作することを特徴とする。両面基板17、18は、従来の多層基板の製造工程に一般的に用いられている上述したベース基板5と同様の素材からなる基板が用いられる。なお、ベース基板部製作工程は、個別の工程を上述したベース基板部2の各製作工程と同様とすることから、個別の構成についての詳細な説明を省略する。

【0055】ベース基板部製作工程は、図11に示した 両面基板17に対して、その基材17aの表裏主面に接 合された導体部17b,17cにフォトリソグラフ処理 を施すことによってそれぞれ所定のパターンニングを行 うとともにエッチング処理を施して図12に示すように 所定の回路パターン19a、19bを形成する。両面基 板17には、同図に示すようにビアホール20aがそれ ぞれ形成される。第1の回路パターン19aと第2の回 路パターン19bとは、上述したベース基板部2の第1

40

配線層12a及び第2配線層14aとにそれぞれ対応する。なお、第2の両面基板18についても、同様にその基材18aの表裏主面の導体部18b, 18cに所定の回路パターン21a、21b及びビアホール22をそれぞれ形成する。これら第1の回路パターン21aと第2の回路パターン21bとは、上述したベース基板部2の第1配線層12b及び第2配線層14bとにそれぞれ対応する。

【0056】ベース基板部製作工程は、図13に示すように2枚の両面基板17、18を例えば中間樹脂材23を介して接合する。ベース基板部製作工程は、これによって図14に示したベース基板中間体24を製作する。ベース基板中間体24は、中間樹脂材23の表裏主面にそれぞれ両面基板17、18により2層の配線層からなる第1のパターン配線層と第2のパターン配線層とが形成されてなる。

【0057】ベース基板部製作工程においては、上述したベース基板部2の製作工程と同様に、ベース基板中間体24に対して平坦化の処理工程が施される。ベース基板部製作工程においては、図15に示すようにベース基板中間体24の表裏主面にそれぞれ熱プレスにより第1の樹脂付銅箔25と第2の樹脂付銅箔26とを接合する。第1の樹脂付銅箔25と第2の樹脂付銅箔26 と第2の樹脂付銅箔25 と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25と第2の樹脂付銅箔25とは、図15に示すように樹脂層25b、26b側を接合面として第2配線層19b、21b上にそれぞれ接着樹脂によって接合される。

【0058】ベース基板部製作工程においては、第1の樹脂付銅箔25と第2の樹脂付銅箔26とに対して研磨加工が施される。ベース基板部製作工程においては、図16に示すように第1の両面基板17側については、第2配線層19bが外方に露出するように第1の樹脂付銅箔25の研磨加工を施すことによって高精度に平坦化されたビルドアップ形成面27を構成する。ベース基板部製作工程においては、第2の両面基板18側については、樹脂層26bにより回路パターン21bが外方に露出されないように第2の樹脂付銅箔26の研磨加工が行われる。ベース基板部製作工程においては、上述した工程を経て、ベース基板部16を製作する。

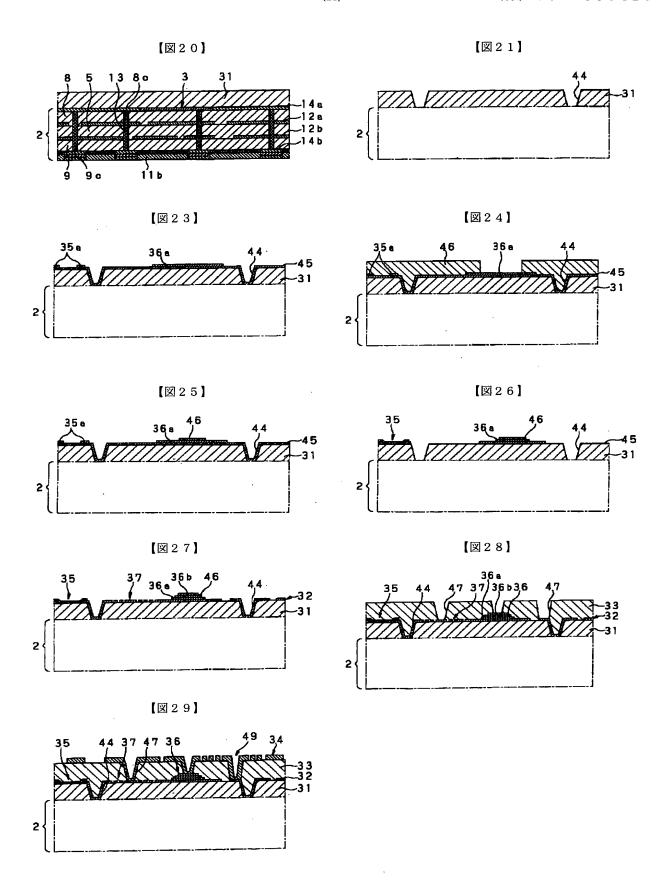

【0059】ベース基板部製作工程は、上述したようにベース基板中間体に対してその表裏主面に樹脂付銅箔を接合した後に、これら樹脂付銅箔に研磨加工を施して平坦化処理を行うようにしたが、かかる工程に限定されるものではない。第3の実施の形態として図17乃至図19に示したベース基板部製作工程は、上述した各製作工程を経て製作されたベース基板中間体15に対してディップコート法によって樹脂材28を塗布形成する工程を有することを特徴とする。すなわち、ベース基板部製作工程においては、ディップ槽29内に適当な溶媒によっ50

て液状に溶かした樹脂材28が貯められおり、図17に 示すようにこのディップ槽29内にベース基板中間体1 5を漬ける工程が施される。

【0060】ベース基板部製作工程においては、ベース基板中間体15が、適当な漬け置き時間を経て適当な引上げ速度を以ってディップ槽29から取り出される。ベース基板部製作工程においては、ディップ槽29から取り出されたベース基板中間体15の表裏主面に、図18に示すように液状樹脂材が硬化して樹脂層28a、28bを同時に形成する。ベース基板部製作工程においては、このようにして樹脂層28a、28bを形成したベース基板中間体15を水平状態に保持してベーキング処理を施し、余分な有機成分を蒸発させる工程を施す。ベース基板部製作工程においては、ベース基板中間体15に対して上述した研磨加工を施して各樹脂層28a、28bを所定量研磨することで、図19に示したベース基板部30を製作する。

【0061】ベース基板部製作工程においては、液状とされた樹脂材28の濃度、漬け置き時間或いは引上げ速度を制御することによってベース基板中間体15に対して所定の膜厚精度の樹脂層28a、28bを形成することが可能とされる。なお、樹脂材28については、例えば方向性化学エッチング法(RIE:Reactive Ion Etching)やプラズマエッチング法(PE:Plasma Etching)等のドライエッチング法により、その平坦化を行うようにしてもよい。

【0062】上述した工程を経て製作されたベース基板部2には、後述するように高周波素子層形成工程を経てビルドアップ形成面3上に多層の高周波回路部4が形成される。高周波回路部4は、図1に示すように第1の絶縁層31と、第1の配線層32と、第2の配線層34とが積層形成されてなる。高周波回路部4は、詳細を後述するように第1の配線層32の厚みtに対して第2の配線層34の厚みTが大きく形成され、第1の配線層32内に詳細を後述する形成工程を経て抵抗素子部35と、キャパシタ素子部36及び高周波用インダクタ素子部37とが形成されてなる。高周波回路部4には、第2の配線層34内に詳細を後述する形成工程を経て低周波用インダクタ素子部38が形成されてなる。

【0063】高周波回路部4は、上述したようにベース 基板部2のビルドアップ形成面3を高精度に平坦化する ことによって、抵抗素子部35、キャパシタ素子部3 6、高周波用インダクタ素子部37或いは低周波用イン ダクタ素子部38が高精度に成膜形成されてなる。一般 的な有機基板は、その表面に形成される導体パターンの 厚みが数十μmと比較的大きく、その上部に成膜形成さ れる厚みが数μmの素子部の精度が劣化する。高周波回 路部4は、上述したように高精度に平坦化されたベース 基板部2のビルドアップ形成面3上に各素子部を高精度 に成膜形成することが可能である。

【0064】高周波回路部4は、図1に示すように第2 の配線層34に形成した電極部39を除いて全体が第1 の保護層40によって被覆されてなる。ベース基板部2 は、ビルドアップ形成面3上に上述した高周波回路部4 を形成するとともに、第2配線層14bを覆った第4の 樹脂付銅箔11の樹脂層11bが除去されて第2配線層 14bに形成した接続電極部41を除いて全体が第2の 保護層42によって被覆されてなる。ベース基板部2と 高周波回路部4とは、モジュール基板1を構成する。モ ジュール基板 1 は、ベース基板 2 のビルドアップ形成面 3と対向する主面(実装面)2a側を実装面として電極 部41を介してマザー基板93に実装されるとともに、 高周波回路部4の第2の配線層34に形成された電極部 39に接続されて高周波 IC90やチップ部品91が実 装されかつ全体がシールドカバー92によって覆われて 図1に示す高周波モジュール装置94を構成する。

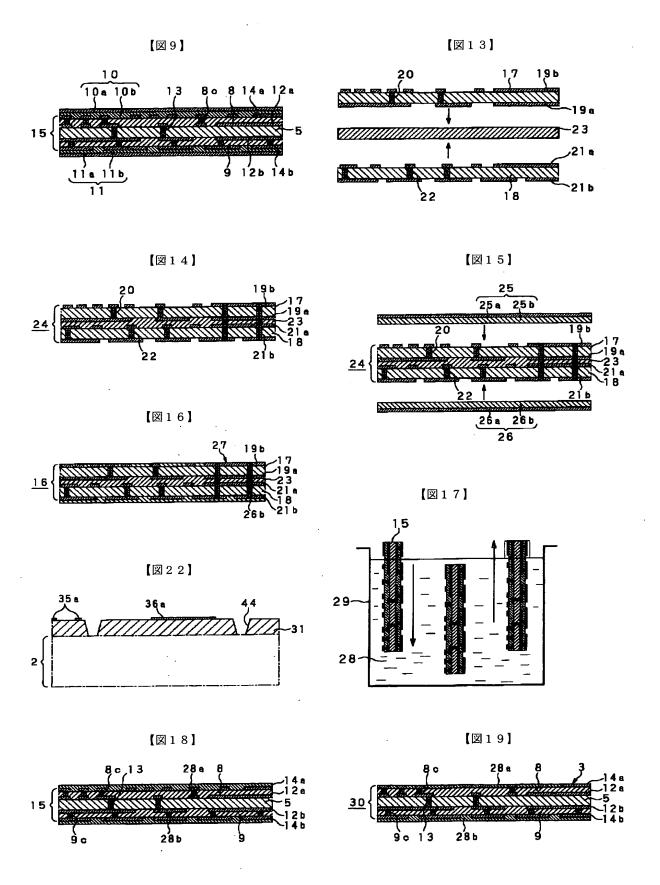

【0065】次に、高周波回路部4の製作工程について、以下図2及び図20乃至図30に示した製作工程図を参照して詳細に説明する。高周波回路部4の製作工程は、上述した工程を経て製作されたベース基板部2の平坦化されたビルドアップ形成面3上に、第1の絶縁層31を形成する第1の絶縁層形成工程s-7と、この第1の絶縁層31上に各素子部を有する第1の配線層32を形成するための下地処理を施す下地処理工程s-8と、第1の配線層32を形成する第1の配線層形成工程s-9とを有してモジュール基板中間体43を製作する。

【0066】高周波回路部4の製作工程は、上述したモジュール基板中間体43に対して、第1の配線層32上に第2の絶縁層33を積層形成する第2の絶縁層形成工程s-11と、電極34を形成する第2の配線層形成工程s-11と、電極部39を除いて第2の配線層形成工程s-11と、電極部39を除いて第2の配線層形成工程s-12とを経てモジュール基板1を製作する。なお、高周波回路部4の製作工程においては、ベース基板部2の第2配線層14bを被覆した樹脂層28bを研磨して電極部41を外方に露出させる研磨工程と、電極部41を除いて第2配線層14bを被覆する第2の保護層42を形成する保護層形成工程とを有する。

【0067】なお、高周波回路部4は、ベース基板部2のビルドアップ形成面3上に形成された第1の配線層3 2と第2の配線層34との2層構造によって構成されるが、さらに多層の配線層によって構成されるようにしてもよい。かかる高周波回路部4においては、内層側配線層に高周波用インダクタ素子部37が成膜形成されるとともに、表層側配線層に低周波用インダクタ素子部38が成膜形成される。

【0068】第1の絶縁層形成工程s-7においては、 いることが好ましく、特 ベース基板部2のビルドアップ形成面3上に絶縁性誘電 50 易なAlが好適である。

材が供給されて、図20に示すように第1の絶縁層31 が成膜形成される。絶縁性誘電材には、ベース基板5と同様に低誘電率で低いTanδ、すなわち高周波特性に優れかつ耐熱性や耐薬品性及び少なくとも160℃以上の高耐熱性に優れた有機基材が用いられる。絶縁性誘電材には、具体的には、ベンゾシクロブテン(BCB)、ポリイミド、ポリノルボルネン(PNB)、液晶ポリマ(LCP)、ビスマレイドトリアジン(BTーレジン)、ポリフェニールエチレン(PPE)或いはエポキシ樹脂やアクリル系樹脂が用いられる。成膜方法としては、塗布均一性、厚み制御性が保持されるスピンコート法、カーテンコート法、ロールコート法或いはディップコート法等が適用される。

【0069】第1の絶縁層形成工程s-7においては、図21に示すようにベース基板部2上に成膜された第1の絶縁層31に対して多数のビアホール44が形成される。各ビアホール44は、ビルドアップ形成面3に露出された第2配線層14aの所定の電極部に対応してそれぞれ形成され、これら電極部を外方へと臨ませる。各ビアホール44は、絶縁性誘電材として感光性樹脂を用いた場合には、所定のパターンニングに形成されたマスクを第1の絶縁層31に取り付けてフォトリソグラフ法により形成される。各ビアホール44は、絶縁性誘電材として非感光性樹脂を用いた場合には、例えばフォトレジストや金等の金属膜等をマスクとして、方向性化学エッチング(RIE:reactive ion etching)等のドライエッチング法によってホール形成が行われる。

【0070】下地処理工程s-8においては、第1の絶縁層31上に例えばスパッタ法等によって後述する第1の配線層32を形成する金属薄膜を薄膜形成し、この金属薄膜にエッチング処理を施して図22に示すように抵抗素子部35の受電極35a及びキャパシタ素子部36の下電極36aを成膜形成する。金属薄膜は、例えばCu、Al、Pt、Au等の金属材料によって成膜形成される。なお、金属薄膜は、第1の絶縁層31との密着性を向上させるために、バリア層として例えばCr、Ni、Ti等の金属薄膜を形成してこれら金属薄膜上に成膜形成するようにしてもよい。

【0071】金属薄膜は、後述する第1の配線層32や40 キャパシタ素子部36の上電極36bをウェットエッチングによってパターン形成する際に、エッチングの選択性が得られることが好ましい。金属薄膜は、後述するように第1の配線層32がCu薄膜に対して硝酸、硫酸及び酢酸系の混合酸からなるエッチング液を用いてウェットエッチングを施されてパターン形成されるので、Cu薄膜で成膜形成された場合には同時にエッチングされてしまう。したがって、金属薄膜は、上述したエッチング液に耐性を有するA1、Pt或いはAuの金属材料を用いることが好ましく、特にパターニング処理が比較的容50 易なA1が好適である

【OO72】金属薄膜は、例えばAlを用いる場合に、 スパッタリング法により2000Å程度の厚みを以って 第1の絶縁層31上に全面に亘って形成される。金属薄 膜には、リソグラフ処理によりフォトレジストをパター ン形成し、リン酸等のエッチング液を用いたウェットエ ッチングによって上述した抵抗素子部35の受電極35 a及びキャパシタ素子部36の下電極36aを形成す る。

27

【0073】第1の配線層形成工程 s - 9 においては、 図23に示すように第1の絶縁層31及び各電極を被覆 する窒化タンタル (TaN) 層45を成膜形成する。T aN層45は、抵抗体として作用するとともに、キャパ シタ素子部36を成膜形成する際に陽極酸化により形成 される酸化タンタル (TaO) 誘電体膜のベースとして 作用する。TaN層45は、例えばスパッタリング法に よって2000Å程度の厚みを以って成膜形成される。 なお、TaN層45は、Ta薄膜であってもよい。

【0074】第1の配線層形成工程 s - 9 においては、 図24に示すようにキャパシタ素子部36の下電極36 aを開口部46aによって外方に臨ませその他の部位を 被覆する陽極酸化用マスク層46が形成される。陽極酸 化用マスク層46は、例えば容易にパターニングが可能 なフォトレジストを用い、次工程の陽極酸化処理時の印 加電圧に対して被覆部位が充分な絶縁性を保持すること が可能であればよく数μ m乃至数十μ mの厚みを以って 形成される。なお、陽極酸化用マスク層46について は、薄膜形成が可能であるその他の絶縁材料、例えば酸 化シリコン材(SiO2)を用いてパターニング形成し てもよい。

【0075】第1の配線層形成工程s-9においては、 陽極酸化用マスク層46を成膜形成した後に陽極酸化処 理を行って、開口部46aから露出したキャパシタ素子 部36の下電極36aに対応するTaN層45を選択的 に陽極酸化する。陽極酸化処理は、例えば電解液として ホウ酸アンモニウムが用いられ、50 v 乃至200 v の 電圧印加が行われる。印加電圧は、陽極酸化用マスク層 46の開口部45aに対応して形成されるTaO誘電体 膜の膜厚を所望の厚みに形成するために適宜調整され る。第1の配線層形成工程 s - 9においては、陽極酸化 用マスク層46を除去することにより開口部46aに対 40 応したTaN層45を選択的に酸化して、図25に示す ように後述するキャパシタ素子部36の誘電体材料とな るTaO層46が形成される。

【0076】第1の配線層形成工程s-9においては、 全面に成膜形成されているTaN層45に例えばフォト リソグラフ処理とドライエッチング処理とを施すことに よって、図26に示すように所望の抵抗体素子部35と、 キャパシタ素子部36の大きさにパターニングする。第 1の配線層形成工程 s - 9においては、上述した処理を 施すことにより、抵抗体素子部35とキャパシタ素子部 50 工程s-11によって、図29に示すように第2の配線

36とを成膜形成するための適宜にパターニングされた TaN層45を同時に形成する。なお、第1の配線層形 成工程s-9においては、上述したTaN層45に陽極 酸化処理を施す際に、陽極酸化用マスク層46を用いず にTaN層45を全面に亘って陽極酸化させた後にTa N+TaO層をパターニングするようにしてもよい。第 1の配線層形成工程 s - 9は、かかる処理を施す場合に 抵抗体素子部35に設けられるTaN層も表面が陽極酸 化されることにより、この酸化膜が保護膜として抵抗体 素子部35を長期的に安定した状態に保持する。

28

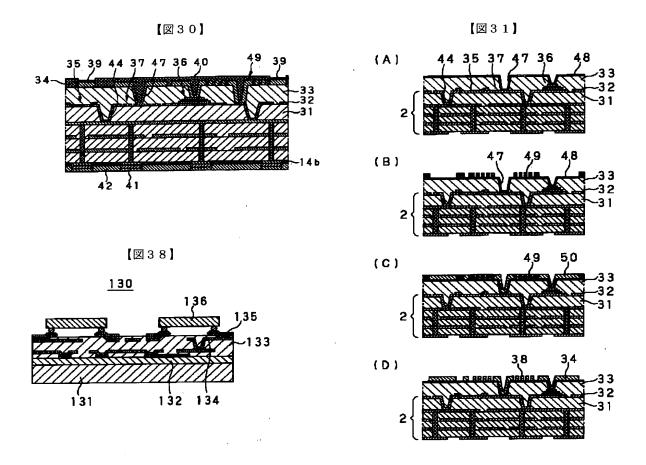

【0077】第1の配線層形成工程s-9においては、 図27に示すように、第1の配線層32と、TaN層4 5を介して下電極36aと対向するキャパシタ素子部3 6の上電極36bと、高周波用インダクタ素子部37と を成膜形成してモジュール基板中間体43を製作する。 第1の配線層32は、髙周波回路部4の第1層を構成す ることから、高周波帯域において損失の小さいCu配線 で構成される。また、第1の配線層32は、例えばメッ キ法、スパッタリング法或いは蒸着法等によって、厚み が約10μmの第1の絶縁層31上に0.2μm乃至5 μmの厚みを以って形成される。第1の配線層32は、 後述する第2の配線層34に対して薄厚の配線層として 形成される。高周波用インダクタ素子部37は、上述し たようにインダクタが、周波数に依存する表皮効果厚み 以上では伝播損失がほとんど変わらずかつ周波数が高け れば高いほど薄くなる表皮効果特性により、薄厚の第1 の配線層32に形成されることによって特性の向上が図 られる。モジュール基板中間体43には、第2の絶縁層 形成工程s-10が施されることにより、図28に示す ように上述した第1の配線層32上に第2の絶縁層33 が積層形成される。第2の絶縁層形成工程 s-10は、 上述した第1の絶縁層形成工程 s - 7と同様の工程であ り、低誘電率で低い t a n δ、すなわち高周波特性に優 れかつ耐熱性や耐薬品性に優れた上述した有機基材が供 給されて、塗布均一性、厚み制御性が保持されるスピン コート法、カーテンコート法、ロールコート法或いはデ ィップコート法等の成膜方法によって成膜形成される。 第2の絶縁層33は、上述したように薄膜形成された第 1の配線層32に形成されることから、高厚み精度を以 って形成することが可能とされる。

【0078】第2の絶縁層形成工程s-10において は、図28に示すように第2の絶縁層33に多数のビア ホール47が形成される。各ビアホール47は、第1の 配線層32に形成された所定の電極部やキャパシタ素子 部36の上電極36b或いは高周波用インダクタ素子部 37をそれぞれ第2の絶縁層33の外方に露出させる。 なお、各ビアホール47も、上述した第1の絶縁層31 のビアホール44と同様に形成される。

【0079】第2の絶縁層33には、第2の配線層形成

層34が形成される。第2の配線層34も、高周波帯域 において損失の小さいCu配線層からなり、また低周波 用インダクタ素子部38が形成されることからこの低周 波用インダクタ素子部38の損失が充分に小さくなるよ うに大きな層厚を以って形成される。すなわち、低周波 用インダクタ素子部38は、上述したようにインダクタ の表皮効果が、周波数に依存する表皮効果厚み以上では 伝播損失がほとんどかわらずかつ周波数が高いほど薄く なる特性があることから、厚みの大きな第2の配線層3 4に形成されることにより特性向上が図られるようにな 10 る。第2の配線層34は、モジュール基板1が高周波モ ジュール装置94に用いられ、低周波用インダクタ素子 部38が例えば数百MHz程度の周波数帯域で機能する 場合に厚みが  $5 \mu$  m以上、好ましくは  $10 \mu$  m以上であ ることが好ましい。

【0080】第2の配線層形成工程s-11は、上述し た第2の配線層34を例えば銅電解メッキ法によって形 成する。銅電解メッキ法による第2の配線層34の形成 方法について、図31に示した工程図を参照して説明す る。銅電解メッキ工程においては、第1の絶縁層34上 に、同図(A)に示すように全面に亘って電解取出用の 電極として作用する厚みが約5000A程度の銅薄膜層 48を成膜形成する。銅電解メッキ工程においては、形 成される銅薄膜層48の密着性の向上を図るために、第 2の絶縁層34上に例えば厚みが約250Å程度のNi 層等のバリア層をあらかじめ形成しておくことが好まし

【0081】銅電解メッキ工程においては、形成された 銅薄膜層48に、同図(B)に示すように、厚みが約1 2μ m程度のメッキ用レジスト層49をパターン形成す る。銅電解メッキ工程においては、銅薄膜層48を電解 取出用電極として電解銅メッキを行って、同図(C)に 示すようにメッキ用レジスト層49の開口部位49aに 約10μm以上の銅メッキ層50をリフトアップ形成す る。銅電解メッキ工程においては、メッキ用レジスト層 49を洗浄除去するとともに、例えばウエットエッチン グ処理を施して同図(D)に示すように不要な銅薄膜層 48を除去することで銅メッキ層50により所定のパタ ーンからなる第2の配線層34を成膜形成する。なお、 銅電解メッキ工程においては、上述したように所定パタ ーンの第2の配線層34とともに低周波用インダクタ素 子部38が成膜形成される。低周波用インダクタ素子部 38も、上述した特性を有する充分な膜厚を以って成膜 形成される。

【0082】第2の配線層34は、図30に示すように 保護層形成工程 s-12により成膜形成される第1の保 護層40によって被覆される。保護層形成工程s-12 は、保護層形成のために一般に用いられる例えばソルダ レジストや層間絶縁層材料等の保護層材が用いられ、ス

の全面を被覆する保護膜層を形成する。保護層形成工程 s-12においては、保護膜層に対してマスクコーティ ング、フォトリソグラフ処理を施して第2の配線層34 の電極部51を開口部として外方に露出させる第1の保 護層40を形成する。第1の保護層40は、その表面が 上述したように実装面4aを構成する。保護層形成工程 s-12においては、追加工工程として露出された電極 部51に無電解Ni-Auメッキ或いはNi-Cuメッ キ等を施して電極形成を行う。

【0083】ベース基板部2のベース基板5には、上述 したように第2の主面5b側に第2配線層14bが形成 され、この第2配線層14bが露出する寸前まで樹脂層 11 bによって被覆されてなる。ベース基板部2には、 上述した工程を経てビルドアップ形成面3上に高周波回 路部4を積層形成した後に、保護層形成工程 s - 12の 前工程で樹脂層11bを研磨する研磨処理が施されて第 2配線層14bが露出される。ベース基板部2には、上 述した保護層形成工程 s - 1 2 において第2の主面 5 b の全面に第2の保護層42が形成される。ベース基板部 2は、第2の保護層42に対してマスクコーティング、 フォトリソグラフ処理を施して電極部41を開口部とし て外方に露出させ、これらに無電解Ni-Auメッキ等 を施して電極形成を行う。

【0084】以上の工程を経て製作されたモジュール基 板1は、上述したように髙周波回路部4の実装面4a上 に、電極部39を介して髙周波IC90やチップ部品9 1がフリップチップ実装法等の適宜の実装方法によって 搭載される。また、モジュール基板1は、ベース基板部 2の実装面2aが、電極部41を介してフリップチップ 実装法や半田ボール等によりマザー基板93に搭載され る。モジュール基板1は、高周波IC90等を実装した 状態において、電磁ノイズの影響を排除するためのシー ルドカバー92が組み付けられて高周波回路部4の実装 面4aが覆われて高周波モジュール装置94を構成す

【0085】ところで、高周波モジュール装置94にお いては、上述したようにモジュール基板1の高周波回路 部4をシールドカバー92によって被覆した構造である ことから、髙周波回路部4上に実装された髙周波IC9 0やチップ部品91から発生した熱がシールドカバー9 2内に籠もって特性に悪影響を及ぼすことがある。 した がって、高周波モジュール装置94には、適宜の放熱構 造を設けることが好ましい。

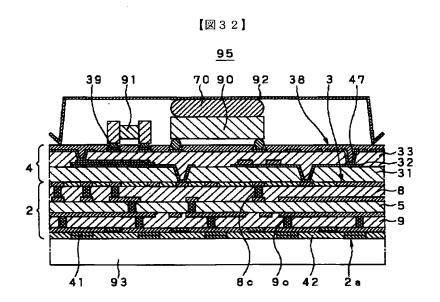

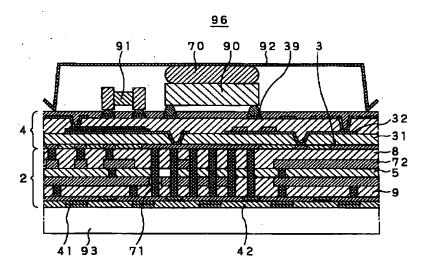

【0086】図32に示した高周波モジュール装置95 は、発熱量が大きな高周波IC90の上面とシールドカ バー92の内面との間に熱伝導性樹脂材70を充填して 放熱構造を構成してなる。高周波モジュール装置95に おいては、高周波IC90からの発熱が熱伝導性樹脂材 70を介してシールドカバー92へと伝達され、このシ ピンコート法等の適宜の方法によって第2の配線層34 50 ールドカバー92を介して放熱されることで熱が内部に 籠もって特性に悪影響を及ぼすことが防止される。な お、高周波モジュール装置95においては、比較的大型 の高周波IC90を熱伝導性樹脂材70とシールドカバ - 92とによって保持することで、機械的な実装剛性の 向上も図られるようになる。

【0087】図33に示した高周波モジュール装置96 は、高周波IC90やチップ部品91から発生する熱を さらに効率的に放熱するように構成してなり、上述した 熱伝導性樹脂材70に加えて高周波IC90の搭載領域 に対応してベース基板部2と高周波回路部4とに連通す 10 る多数の冷却用ビアホール71が形成されてなる。各冷 却用ビアホール71は、ベース基板部2や高周波回路部 4に上述した回路接続用の各ビアホールを形成する際に 同様の工程によって形成される。

【0088】高周波モジュール装置96においては、高 周波IC90から発生した熱が、上述したように熱伝導 性樹脂材70を介してシールドカバー92から放熱され るとともに、冷却用ビアホール71を介してベース基板 部2の底面に伝達されて外部へと放熱される。 高周波モ ジュール装置96は、モジュール基板1の上下からの放 20 や配線層を有する高周波回路部が直接形成されること 熱が行われることでより効率的な放熱が行われるように なる。なお、髙周波モジュール装置96は、冷却用ビア ホール71のみによって放熱構造を構成するようにして もよい。また、高周波モジュール装置96は、例えばべ ース基板5に形成される銅箔部72が例えば50nmと 厚みを大きくして形成したものを用いるようにし、この 銅箔部72に対して冷却用ビアホール71がそれぞれ接 続されるようにすることによってベース基板5からの放 熱が行われるようにしてもよい。

【0089】図34に示した髙周波モジュール装置97 は、例えば銅や42アロイ等の導電性が良好なメタルコ アを基材としたベース基板73によってベース基板部2 が形成されてなる。高周波モジュール装置97は、この ベース基板73に対して上述した多数の冷却用ビアホー ル71がそれぞれ接続されるように構成する。高周波モ ジュール装置97においては、冷却用ビアホール71を 介してベース基板73からの放熱も行われ、上述した放 熱用の導電樹脂材70や冷却用ビアホール71の構成と によってさらに効率的な放熱が行われるようになり信頼 性の向上が図られる。

## [0090]

【発明の効果】以上詳細に説明したように、本発明によ れば、平坦化されたビルドアップ形成面を有するベース 基板部に受動素子を成膜形成した高周波回路部を積層形 成してなり、高周波回路部の内層側配線層に高周波用イ ンダクタ素子が成膜形成されるとともに内層側配線層よ りも層厚に形成される表層側配線層に低周波用インダク タ素子が成膜形成されることから、各インダクタ素子が 各配線層の厚みに伴う損失特性と表皮効果特性にマッチ ングして特性向上が図られるようになる。本発明によれ 50 ば、内層側配線層を層薄とすることによって、表層側配 線部に高精度の受動素子の薄膜形成を可能とし、小型 化、薄型化が図られるとともに高精度化及び高機能化が 図られるようになる。

【0091】本発明によれば、ベース基板部に電源やグ ランド部等の配線部や制御系の配線部が構成されるとと もに高周波回路部に高周波信号回路部が構成されること で、両者の電気的分離が図られ電気的干渉の発生が抑制 されて特性の向上が図られた廉価なモジュール基板及び 高周波モジュール装置が得られるようになる。本発明に よれば、ベース基板部に充分な面積を有する電源やグラ ンド部の配線を形成することが可能であることから、レ ギュレーションの高い電源供給が行われるモジュール基 板及び高周波モジュール装置が得られるようになる。

【0092】本発明によれば、特に絶縁性を有するとと もに比較的廉価な有機基板をベース基板として用いてベ ース基板部の主面に高精度の平坦化処理を施してビルド アップ形成面として構成し、このビルドアップ形成面上 に薄膜技術或いは厚膜技術により形成される高周波素子 で、高周波回路部の層内に高精度でかつ高周波特性が良 好な受動素子が簡易な工程によって形成される。本発明 によれば、廉価な材料からなるベース基板上に従来の多 層基板のプロセスと同様にして多層の配線層を形成して ベース基板部が低コストで形成されることで、全体コス トの低減が図られたモジュール基板及び高周波モジュー ル装置が得られるようになる。

## 【図面の簡単な説明】

【図1】本発明にかかる高周波モジュール装置の要部縦 断面図である。

【図2】同髙周波モジュール装置に備えられるモジュー ル基板の製造工程図である。

【図3】同モジュール基板に用いられるベース基板の縦 断面図である。

【図4】同ベース基板に対するパターニング工程説明図 である。

【図5】第1の樹脂付銅箔及び第2の樹脂付銅箔の接合 工程説明図である。

【図6】ビア形成の工程説明図である。

【図7】第1のパターン配線層及び第2のパターン配線 40 層の形成工程説明図である。

【図8】第3の樹脂付銅箔及び第4の樹脂付銅箔の接合 工程説明図である。

【図9】第3の樹脂付銅箔及び第4の樹脂付銅箔を接合 した状態の工程説明図である。

【図10】第3の樹脂付銅箔及び第4の樹脂付銅箔の研 磨工程説明図である。

【図11】モジュール基板に用いられる他のベース基板 の縦断面図である。

【図12】同ベース基板に対するパターニング工程説明

図である。

【図13】ベース基板の接合工程説明図である。

【図14】ベース基板中間体の縦断面図である。

【図15】ベース基板中間体に樹脂付銅箔を接合する工 程説明図である。

【図16】研磨処理を施したベース基板部の縦断面図である。

【図17】ディップ工程の説明図である。

【図18】ベース基板中間体の縦断面図である。

【図19】研磨処理を施したベース基板部の縦断面図で 10 ある。

【図20】ベース基板部に対して第1の絶縁層を形成する第1の絶縁層形成工程の説明図である。

【図21】ビアホール形成工程の説明図である。

【図22】抵抗素子部の受電極及びキャパシタ素子部の下電極を成膜形成する工程の説明図である。

【図23】窒化タンタル層を成膜形成する工程の説明図である。

【図24】陽極酸化用マスク層を形成する工程の説明図である。

【図25】 TaO層を形成する工程の説明図である。

【図26】抵抗体素子部とキャパシタ素子部のパターニング工程の説明図である。

【図27】モジュール基板中間体の縦断面図である。

【図28】ビアホールを形成する工程の説明図である。

【図29】第2の配線層を形成する工程の説明図である

【図30】モジュール基板の縦断面図である。

【図31】第2の配線層を形成する銅電解メッキ法の工 程説明図である。

【図32】放熱構造を備えた高周波モジュール装置の要 部縦断面図である。

【図33】他の放熱構造を備えた高周波モジュール装置の要部縦断面図である。

【図34】他の放熱構造を備えた高周波モジュール装置の要部縦断面図である。

【図35】スーパーヘテロダイン方式による高周波送受\*

\*信回路の構成図である。

【図36】ダイレクトコンバージョン方式による高周波 送受信回路の構成図である。

34

【図37】従来の高周波送受信モジュールに備えられる インダクタ部の説明図である。

【図38】従来のシリコン基板を用いた高周波送受信モジュールの縦断面図である。

【図39】従来のガラス基板を用いた高周波送受信モジュールの縦断面図である。

【図40】従来のモジュール基板をインターポーザ基板 に実装したパッケージの縦断面図である。

#### 【符号の説明】

1 モジュール基板、2 ベース基板部、3 ビルドア ップ形成面、4 高周波回路部、5 ベース基板、6 第1のパターン配線層、7 第2のパターン配線層、8 乃至11 樹脂付銅箔、12 第1層パターン配線層、 13 ビアホール、14 第2層配線層、15 ベース 基板部中間体、16 ベース基板部、17,18 両面 基板、19 回路パターン、20 ビアホール、21 20 回路パターン、22 ビアホール、23 中間樹脂部 材、24 ベース基板部中間体、25,26 樹脂付銅 箔、27 ビルドアップ形成面、28 樹脂層、29 ディップ槽、30 ベース基板部、31 第1の絶縁 層、32 第1の配線層、33第2の絶縁層、34 第 2の配線層、35 抵抗体素子部、36 キャパシタ素 子部、37 高周波用インダクタ素子部、38 低周波 用インダクタ素子部、39 電極部、40 第1の保護 層、41 電極部、42 第2の保護層、43モジュー ル基板中間体、44 ビアホール、45 窒化タンタル 30 層 (TaN層)、46 酸化タンタル層 (TaO層)、 47 ビアホール、48 銅薄膜層、49 メッキレジ スト層、50 銅メッキ層、70 熱伝導性樹脂材、7 1 放熱用ビアホール、72 銅箔部、73 ベース基 板、90 高周波IC、91チップ部品、92 シール ドカバー、93 マザー基板、94万至97 高周波モ ジュール装置

【図3】

【図11】

【図4】

【図12】

【図33】

【図34】

【図39】

# · 【図40】

# 150

# フロントページの続き

(51) Int. C1.

識別記号

FΙ

テーマコード(参考)

HO1L 23/12 301

H O 1 L 23/12

В.

(72) 発明者 中山 浩和

東京都品川区北品川6丁目7番35号 ソニ

一株式会社内

Fターム(参考) 5E346 AA02 AA13 AA14 AA15 AA43

BB06 CC08 CC09 CC10 CC13

CC16 CC21 CC32 DD03 DD12

DD17 DD24 DD32 DD33 DD47

DD48 EE32 EE33 FF07 FF14

FF18 GG15 GG17 GG22 HH04

HH06 HH17 HH22 HH24 HH32